- 您現在的位置:買賣IC網 > PDF目錄373969 > AD9858 (Analog Devices, Inc.) 1 GSPS Direct Digital Synthesizer PDF資料下載

參數資料

| 型號: | AD9858 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | XO, clock |

| 英文描述: | 1 GSPS Direct Digital Synthesizer |

| 中文描述: | 1 GSPS的直接數字頻率合成器 |

| 文件頁數: | 25/32頁 |

| 文件大小: | 1412K |

| 代理商: | AD9858 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

AD9858

Register Bit Descriptions

Rev. A | Page 25 of 32

Control Function Register (CFR)

The CFR is comprised of four bytes located in parallel addresses

0x03 to 0x00. The CFR is used to control the various functions,

features, and modes of the AD9858. The functionality of each

bit is detailed below. Note that the register bits are identified

according to their serial register bit locations beginning with the

most significant bit.

CFR<31:30>: Frequency-Detect Mode Charge Pump Current

These bits are used to set the scale factor for the frequency-

detect mode charge pump output current per Table 7. The

charge pump delivers the scaled output current when the

control logic forces the charge pump into its frequency detect

operating mode. The charge pump’s baseline output current

(I

CP0

) is determined by the external CPISET resistor and is

given by

T

1.24/CPISE

I

CP0

=

The recommended nominal value of the CPISET resistor is

2.4 k, which yields a baseline current of 500 μA.

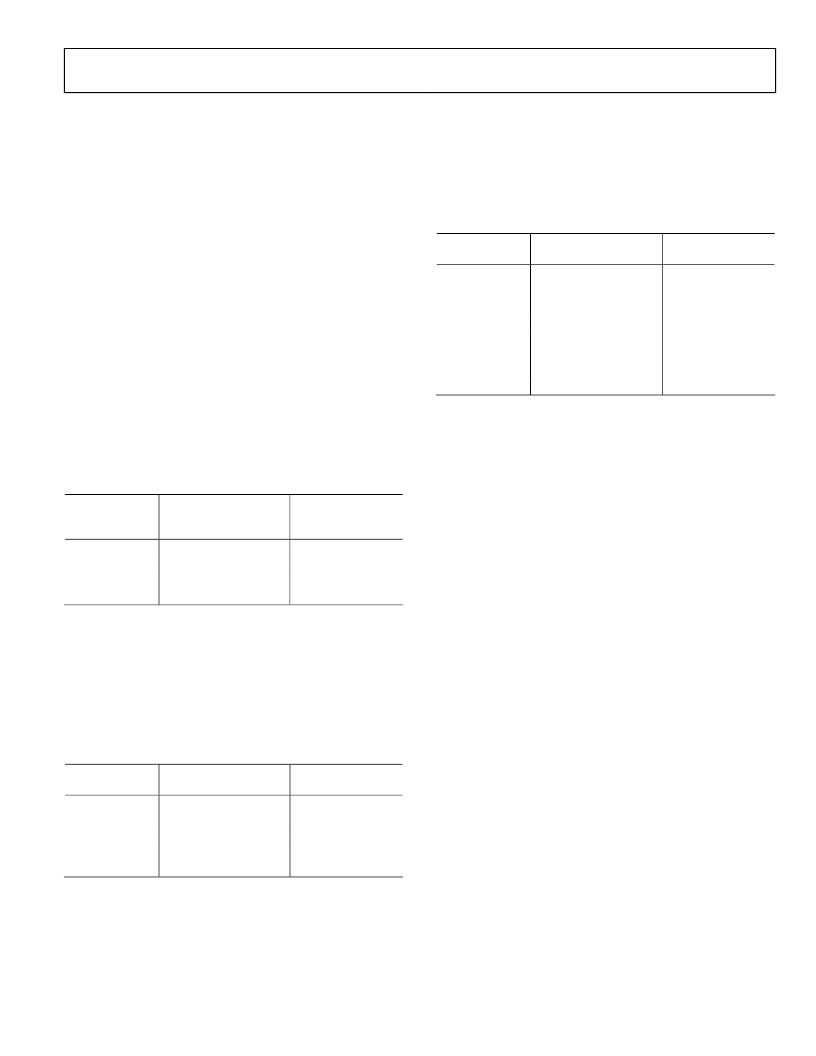

Table 7.

CFR<31:30>

Scale Value

00b

0

01b

2

10b

3

11b

4

Frequency-Detect

Charge Pump

Notes

I

OUT

= 0 (Default)

I

OUT

= 20 × I

CP0

I

OUT

= 40 × I

CP0

I

OUT

= 60 × I

CP0

CFR<29:27>: Final Closed-Loop Mode

Charge Pump Output Current

These bits are used to set the scale factor for the final closed-

loop mode charge pump output current per Table 8. The charge

pump delivers the scaled output current when the control logic

forces the charge pump into its final closed-loop mode.

Table 8.

CFR<29:27>

CP Scale Value

0xxb

0

100b

1

101b

2

110b

3

111b

4

Final Closed-Loop

Notes

I

OUT

= 0

(

Default)

I

OUT

= I

CP0

I

OUT

= 2 × I

CP0

I

OUT

= 3 × I

CP0

I

OUT

= 4 × I

CP0

CFR<26:24>: Wide Closed-Loop Charge Pump

Output Current

These bits are used to set the scale factor for the wide closed-

loop charge pump output current, see Table 9. The charge pump

delivers the scaled output current when the control logic forces

the charge pump into its wide closed-loop operating mode.

Table 9.

CFR<26:24>

CP Scale Value

000b

0

001b

2

010b

4

011b

6

100b

8

101b

10

110b

12

111b

14

Wide Closed-Loop

Notes

I

OUT

= 0

(

Default

)

I

OUT

= 2 × I

CP0

I

OUT

= 4 × I

CP0

I

OUT

= 6 × I

CP0

I

OUT

= 8 × I

CP0

I

OUT

= 10 × I

CP0

I

OUT

= 12 × I

CP0

I

OUT

= 14 × I

CP0

CFR<23>: AutoClear Frequency Accumulator Bit

When CFR<23> = 0 (default), a new delta frequency word is

applied to the input of the accumulator and added to the

currently stored value.

When CFR<23> = 1, this bit automatically synchronously clears

(loads zeros into) the frequency accumulator for one cycle upon

reception of the FUD sequence indicator.

CFR<22>: AutoClear Phase Accumulator Bit

When CFR<22> = 0 (default), a new frequency tuning word is

applied to the input of the phase accumulator and added to the

currently stored value.

When CFR<22> = 1, this bit automatically synchronously clears

(loads zeros into) the phase accumulator for one cycle upon

reception of the FUD sequence indicator.

CFR<21>: Load Delta-Frequency Timer

When CFR<21> = 1 (default), the contents of the delta

frequency ramp rate word are loaded into the ramp rate timer

(down counter) upon detection of a FUD sequence.

When CFR<21> = 0, the contents of the delta frequency ramp

rate word are loaded into the ramp rate timer upon timeout

with no regard to the state of the FUD sequence indicator (i.e.,

the FUD sequence indicator is ignored).

CFR<20>: Clear Frequency Accumulator Bit

When CFR<20> = 1, the frequency accumulator is

synchronously cleared and is held clear until CFR<20> is

returned to a Logic 0 state (default).

相關PDF資料 |

PDF描述 |

|---|---|

| AD9858FDPCB | 1 GSPS Direct Digital Synthesizer |

| AD9859 | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9859YSV | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9859YSV-REEL7 | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9862PCB | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9858/FDPCB | 制造商:Analog Devices 功能描述:EVAL KIT FOR FRACTIONAL DIVIDER EVAL BD - Bulk |

| AD9858/PCBZ | 功能描述:BOARD EVAL FOR AD9858 RoHS:是 類別:編程器,開發系統 >> 評估演示板和套件 系列:- 標準包裝:1 系列:PSoC® 主要目的:電源管理,熱管理 嵌入式:- 已用 IC / 零件:- 主要屬性:- 次要屬性:- 已供物品:板,CD,電源 |

| AD9858/TLPCB | 制造商:Analog Devices 功能描述:NCO/DDS, 1GSPS DIRECT DGTL SYNTHESIZER - Bulk |

| AD9858/TLPCBZ | 制造商:Analog Devices 功能描述:EVAL BOARD - Bulk |

| AD9858BSV | 制造商:Rochester Electronics LLC 功能描述:1000 MHZ DDS/DAC - Bulk 制造商:Analog Devices 功能描述:1GHZ DDS/DAC SMD 9858 TQFP100 制造商:Analog Devices 功能描述:Frequency Synthesizer,AD9858 1GHz TQFP |

發布緊急采購,3分鐘左右您將得到回復。