- 您現在的位置:買賣IC網 > PDF目錄373969 > AD9858 (Analog Devices, Inc.) 1 GSPS Direct Digital Synthesizer PDF資料下載

參數資料

| 型號: | AD9858 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | XO, clock |

| 英文描述: | 1 GSPS Direct Digital Synthesizer |

| 中文描述: | 1 GSPS的直接數字頻率合成器 |

| 文件頁數: | 26/32頁 |

| 文件大小: | 1412K |

| 代理商: | AD9858 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁第29頁第30頁第31頁第32頁

AD9858

CFR<19>: Clear Phase Accumulator Bit

Rev. A | Page 26 of 32

When CFR<19> = 1, the phase accumulator is synchronously

cleared and is held clear until CFR<19> is returned to a Logic 0

state (default).

CFR<18>: Not Used.

CFR<17>: PLL Fast-Lock Enable Bit

When CFR<17> = 0 (default), the PLL’s fast-lock algorithm is

disabled.

When CFR<17> = 1, the PLL’s fast-lock algorithm is active.

CFR<16>

This bit allows the user to control whether or not the PLL’s fast-

locking algorithm uses the tuning word value to determine

whether or not to enter fast-locking mode.

When CFR<16> = 0 (default), the PLL’s fast-locking algorithm

considers the relationship between the programmed frequency

tuning word and the instantaneous frequency as part of the

locking process.

When CFR<16> = 1, the PLL’s fast-locking algorithm does not

use the frequency tuning word as part of the locking process.

CFR<15>: Frequency Sweep Enable Bit

When CFR<15> = 0 (default), the device is in the single-

tone mode.

When CFR<15> = 1, the device is in the frequency-

sweep mode.

CFR<14>: Sine/Cosine Select Bit

When CFR<14> = 0 (default), the angle-to-amplitude

conversion logic employs a cosine function.

When CFR<14> = 1, the angle-to-amplitude conversion logic

employs a sine function.

CFR<13>: Charge Pump Current Offset Bit

When CFR<13> = 0 (default), the charge pump operates with

normal current settings.

When CFR<13> = 1, the charge pump operates with offset

current settings (see charge pump description).

CFR<12:11>: Phase Detector Reference

Input Frequency Divider Ratio

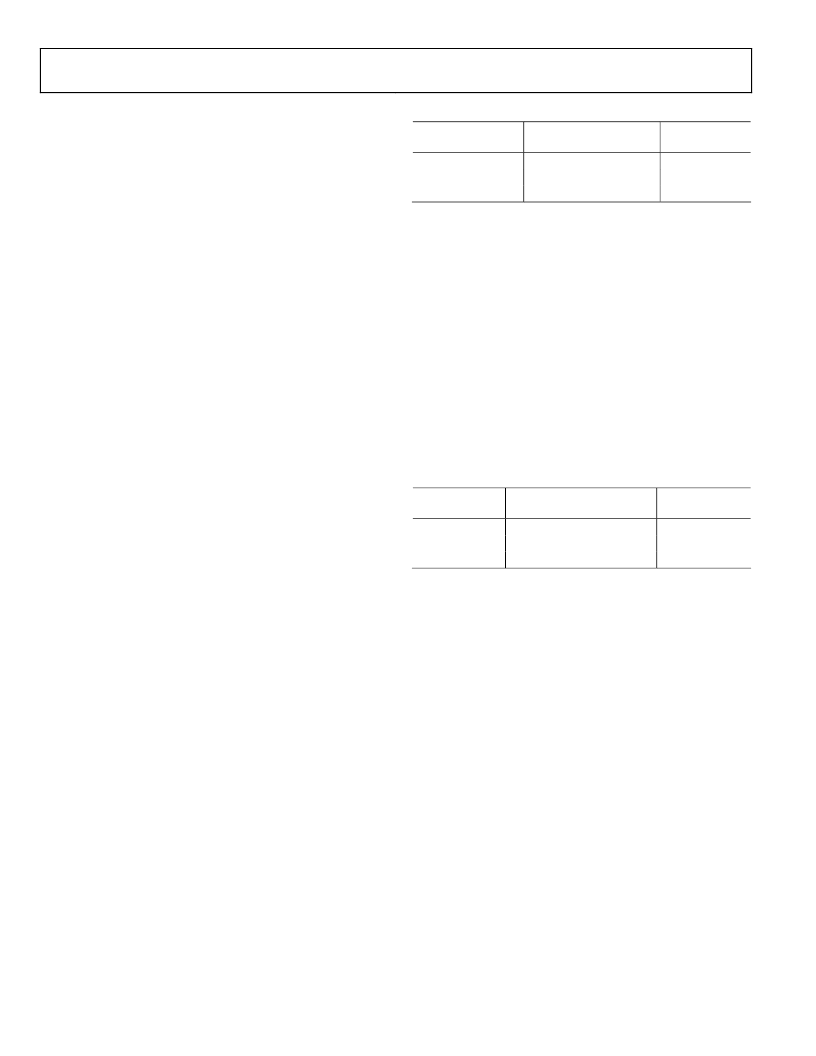

These bits set the phase detector divide value per Table 10.

Table 10.

CFR<12:11>

00b

01b

1xb

Phase Detector

Divider Ratio (N)

1

2

4

Notes

Default Value

LSB Ignored

CFR<10>: Charge Pump Polarity Select Bit

When CFR<10> = 0 (default), the charge pump is set up for

operation with a ground-referenced VCO. In this mode, the

charge pump sources current when the frequency at PD

IN

is

less

than the frequency at DIV

IN

. It sinks current when the opposite

is true.

When CFR<10> = 1, the charge pump is set up for a supply-

referenced VCO. In this mode, the charge pump’s source/sink

operation is opposite that for a ground-referenced VCO.

CFR<9:8>: Phase Detector Feedback

Input Frequency Divider Ratio

These bits set the phase detector divide value per Table 11.

Table 11.

CFR<9:8>

Ratio (M)

00b

1

01b

2

1xb

4

CFR<7>: Not Used

Phase Detector Divider

Notes

Default value

LSB ignored

CFR<6>: Disable Bit for the 2 GHz REFCLK Divider

When CFR<6> = 0 (default), the REFCLK divide-by-2 function

is not bypassed. REFCLK input can be up to 2 GHz.

When CFR<6> = 1, the REFCLK divide-by-2 function is

disabled. REFCLK input must be no more than 1 GHz.

CFR<5>: SYNCLK Disable Bit

When CFR<5> = 0 (default), the SYNCLK pin is active.

When CFR<5> = 1, the SYNCLK pin assumes a static Logic 0

state (disabled). In this state, the pin drive logic is shut down to

keep noise generated by the digital circuitry at a minimum.

However, the synchronization circuitry remains active

(internally) to maintain normal device timing.

CFR<4:2>: Power-Down Bits

Active high (Logic 1) powers down the respective function.

Writing a Logic 1 to all three bits causes the device to enter full-

sleep mode.

CFR<4> is used to shut down the analog mixer stage

(default = 1).

相關PDF資料 |

PDF描述 |

|---|---|

| AD9858FDPCB | 1 GSPS Direct Digital Synthesizer |

| AD9859 | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9859YSV | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9859YSV-REEL7 | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9862PCB | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9858/FDPCB | 制造商:Analog Devices 功能描述:EVAL KIT FOR FRACTIONAL DIVIDER EVAL BD - Bulk |

| AD9858/PCBZ | 功能描述:BOARD EVAL FOR AD9858 RoHS:是 類別:編程器,開發系統 >> 評估演示板和套件 系列:- 標準包裝:1 系列:PSoC® 主要目的:電源管理,熱管理 嵌入式:- 已用 IC / 零件:- 主要屬性:- 次要屬性:- 已供物品:板,CD,電源 |

| AD9858/TLPCB | 制造商:Analog Devices 功能描述:NCO/DDS, 1GSPS DIRECT DGTL SYNTHESIZER - Bulk |

| AD9858/TLPCBZ | 制造商:Analog Devices 功能描述:EVAL BOARD - Bulk |

| AD9858BSV | 制造商:Rochester Electronics LLC 功能描述:1000 MHZ DDS/DAC - Bulk 制造商:Analog Devices 功能描述:1GHZ DDS/DAC SMD 9858 TQFP100 制造商:Analog Devices 功能描述:Frequency Synthesizer,AD9858 1GHz TQFP |

發布緊急采購,3分鐘左右您將得到回復。