- 您現在的位置:買賣IC網 > PDF目錄373969 > AD9864 (Analog Devices, Inc.) IF Digitizing Subsystem PDF資料下載

參數資料

| 型號: | AD9864 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | IF Digitizing Subsystem |

| 中文描述: | 中頻數字化子系統 |

| 文件頁數: | 4/44頁 |

| 文件大小: | 1984K |

| 代理商: | AD9864 |

第1頁第2頁第3頁當前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

AD9864

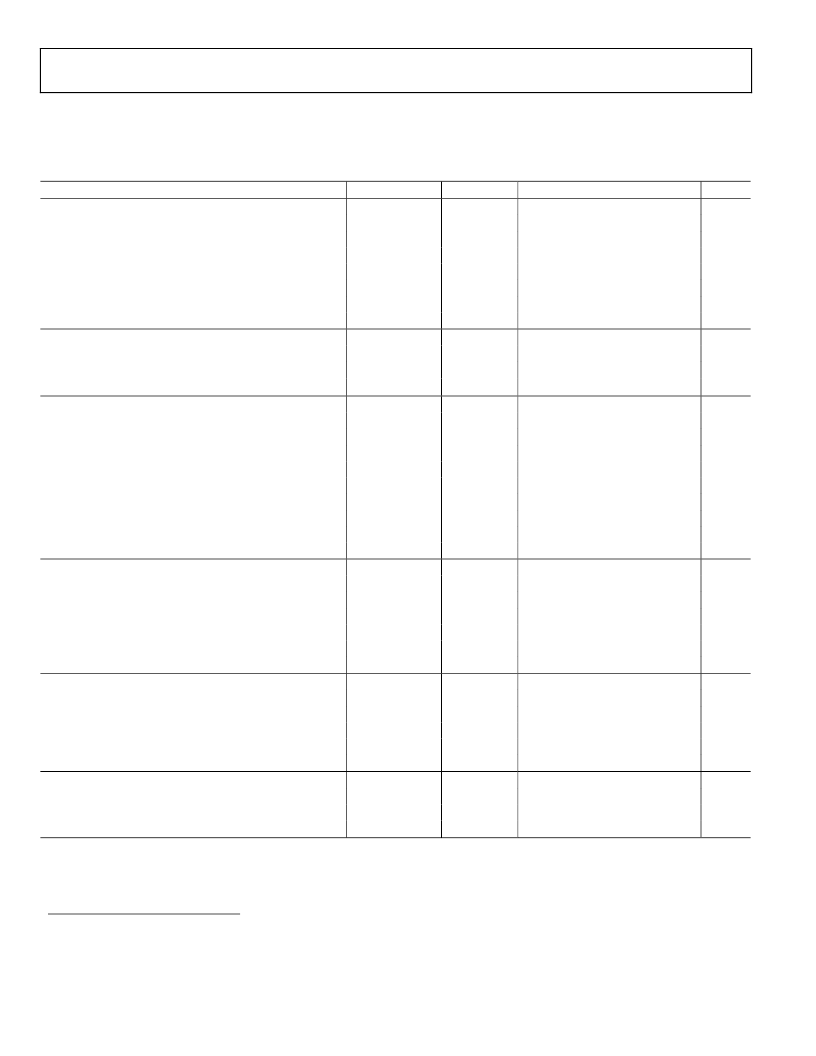

AD9864 SPECIFICATIONS

Table 1. VDDI = VDDF = VDDA = VDDC = VDDL = VDDH = 2.7 V to 3.6 V, VDDQ = VDDP = 2.7 V to 5.5 V, f

CLK

= 18 MSPS,

f

IF

= 109.65 MHz, f

LO

= 107.4 MHz, f

REF

= 16.8 MHz, unless otherwise noted. Standard operating mode: VGA at minimum attenuation

setting, synthesizers in normal (not fast acquire) mode, decimation factor = 900, 16-bit digital output, and 10 pF load on SSI output pins.

Parameter

Temperature

SYSTEM DYNAMIC PERFORMANCE

1

SSB Noise Figure @ Minimum VGA Attenuation

2, 3

Full

@ Maximum VGA Attenuation

2,3

Full

Dynamic Range with AGC Enabled

2,3

Full

IF Input Clip Point @ Maximum VGA Attenuation

3

Full

@ Minimum VGA Attenuation

3

Full

Input Third Order Intercept (IIP3)

Full

Gain Variation over Temperature

Full

LNA + MIXER

Maximum RF and LO Frequency Range

Full

LNA Input Impedance

25°C

Mixer LO Input Resistance

25°C

LO SYNTHESIZER

LO Input Frequency

Full

LO Input Amplitude

Full

FREF Frequency (for Sinusoidal Input Only)

Full

FREF Input Amplitude

Full

FREF Slew Rate

Full

Minimum Charge Pump Current @ 5 V

4

Full

Maximum Charge Pump Current @ 5 V

4

Full

Charge Pump Output Compliance

5

Full

Synthesizer Resolution

Full

CLOCK SYNTHESIZER

CLK Input Frequency

Full

CLK Input Amplitude

Full

Minimum Charge Pump Output Current

4

Full

Maximum Charge Pump Output Current

4

Full

Charge Pump Output Compliance

5

Full

Synthesizer Resolution

Full

Σ- ADC

Resolution

Full

Clock Frequency (f

CLK

)

Full

Center Frequency

Full

Pass-Band Gain Variation

Full

Alias Attenuation

Full

GAIN CONTROL

Programmable Gain Step

Full

AGC Gain Range

Full

GCP Output Resistance

Full

Rev. 0 | Page 4 of 44

Test Level

IV

IV

IV

IV

IV

IV

IV

IV

V

V

IV

IV

IV

IV

IV

VI

VI

VI

IV

IV

IV

VI

VI

VI

VI

IV

IV

V

IV

IV

V

V

IV

Min

91

–20

–32

–12

300

7.75

0.3

8

0.3

7.5

0.4

6.25

13

0.3

0.4

2.2

16

13

80

50

Typ

7.5

13

95

–19

–31

–7.0

0.7

500

370||1.4

1

0.67

5.3

0.67

5.3

f

CLK

/8

16

12

72.5

Max

9.5

2

300

2.0

25

3

VDDP – 0.4

26

VDDC

VDDQ – 0.4

24

26

1.0

95

Unit

dB

dB

dB

dBm

dBm

dBm

dB

MHz

||pF

k

MHz

V p-p

MHz

V p-p

V/μs

mA

mA

V

kHz

MHz

V p-p

mA

mA

V

kHz

Bits

MHz

MHz

dB

dB

dB

dB

k

1

This includes 0.9 dB loss of matching network.

2

AGC with DVGA enabled.

3

Measured in 10 kHz bandwidth.

4

Programmable in 0.67 mA steps.

5

Voltage span in which LO (or CLK) charge pump output current is maintained within 5% of nominal value of VDDP/2 (or VDDQ/2).

相關PDF資料 |

PDF描述 |

|---|---|

| AD9864-EB | IF Digitizing Subsystem |

| AD9864BCPZ | IF Digitizing Subsystem |

| AD9864BCPZRL | IF Digitizing Subsystem |

| AD9866BCPRL | Broadband Modem Mixed Signal Front End |

| AD9866CHIPS | Broadband Modem Mixed Signal Front End |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9864BCP | 制造商:Analog Devices 功能描述:IF SUBSYS 48LFCSP EP - Bulk |

| AD9864BCPZ | 功能描述:IC IF SUBSYSTEM GEN-PURP 48LFCSP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點:- 封裝/外殼:48-TQFP 裸露焊盤 供應商設備封裝:48-TQFP 裸露焊盤(7x7) 包裝:托盤 |

| AD9864BCPZ | 制造商:Analog Devices 功能描述:IC, IF SUBSYSTEM, 16-24BIT, 6.8KHZ-270KH |

| AD9864BCPZRL | 功能描述:IC IF SUBSYSTEM GEN-PURP 48LFCSP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點:- 封裝/外殼:48-TQFP 裸露焊盤 供應商設備封裝:48-TQFP 裸露焊盤(7x7) 包裝:托盤 |

| AD9864-EB | 制造商:Analog Devices 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。