- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373969 > AD9866 (Analog Devices, Inc.) Broadband Modem Mixed Signal Front End PDF資料下載

參數(shù)資料

| 型號: | AD9866 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Broadband Modem Mixed Signal Front End |

| 中文描述: | 寬帶調(diào)制解調(diào)器混合信號前端 |

| 文件頁數(shù): | 36/48頁 |

| 文件大小: | 1647K |

| 代理商: | AD9866 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當前第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

AD9866

Rev. 0 | Page 36 of 48

0

1.0V

TO

ADCs

REFT

REFB

C1

0.1

μ

F

C2

10

μ

F

C3

0.1

μ

F

C4

μ

F

C1

C4

C2

C3

TOP

VIEW

AGC TIMING CONSIDERATIONS

When implementing a digital AGC timing loop, it is important

to consider the Rx path latency and settling time of the Rx path

in response to a change in gain setting. Figure 21 and Figure 24

show the RxPGA’s settling response to a 60 dB and 5 dB change

in gain setting when using the Tx[5:0] or PGA[5:0] port. While

the RxPGA settling time may also show a slight dependency on

the LPF’s cutoff frequency, the ADC’s pipeline delay along with

the ADIO bus interface presents a more significant delay. The

amount of delay or latency depends on whether a half- or full-

duplex is selected. An impulse response at the RxPGA’s input

can be observed after 10.0 ADC clock cycles (1/f

ADC

) in the case

of a half-duplex interface and 10.5 ADC clock cycles in the case

of a full-duplex interface. This latency along with the RxPGA

settling time should be considered to ensure stability of the

AGC loop.

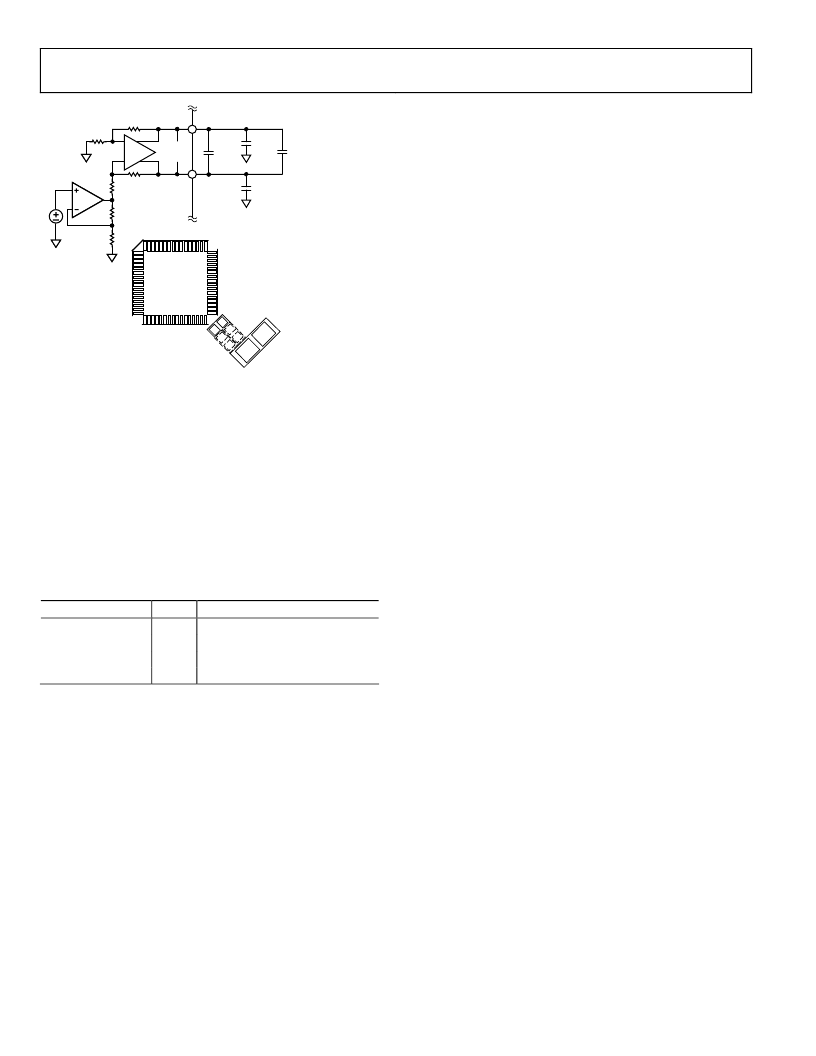

Figure 75. ADC Reference and Decoupling

The ADC has an internal voltage reference and reference ampli-

fier as shown in Figure 75. The internal band gap reference

generates a stable 1 V reference level that is converted to a

differential 1 V reference centered about mid-supply (AVDD/2).

The outputs of the differential reference amplifier are available

at the REFT and REFB pins and

must

be properly decoupled for

optimum performance. The REFT and REFB pins are conven-

iently situated at the corners of the CSP package such that C1

(0603 type) can be placed directly across its pins. C3 and C4 can

be placed underneath C1, and C2 (10 μF tantalum) can be

placed furthest from the package.

Table 21. SPI Registers for Rx ADC

Address (Hex)

Bit

Description

0x04

(5)

Duty cycle restore circuit

(4)

ADC clock from PLL

0x07

(4)

ADC low power mode

0x13

(2:0)

ADC power bias adjust

相關PDF資料 |

PDF描述 |

|---|---|

| AD9866-EB | Broadband Modem Mixed Signal Front End |

| AD9866BCP | Broadband Modem Mixed Signal Front End |

| AD9870 | IF Digitizing Subsystem |

| AD9870EB | IF Digitizing Subsystem |

| AD9873 | Analog Front End Converter for Set-Top Box, Cable Modem |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AD9866BCP | 制造商:Analog Devices 功能描述:Mixed Signal Front End 64-Pin LFCSP EP 制造商:Analog Devices 功能描述:12BIT MIXED SIGNAL CONVERTER 9866 |

| AD9866BCPRL | 制造商:Analog Devices 功能描述:Mixed Signal Front End 64-Pin LFCSP EP T/R |

| AD9866BCPZ | 功能描述:IC PROCESSOR FRONT END 64LFCSP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點:- 封裝/外殼:48-TQFP 裸露焊盤 供應商設備封裝:48-TQFP 裸露焊盤(7x7) 包裝:托盤 |

| AD9866BCPZRL | 功能描述:IC PROCESSOR FRONT END 64LFCSP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點:- 封裝/外殼:48-TQFP 裸露焊盤 供應商設備封裝:48-TQFP 裸露焊盤(7x7) 包裝:托盤 |

| AD9866CHIPS | 制造商:AD 制造商全稱:Analog Devices 功能描述:Broadband Modem Mixed Signal Front End |

發(fā)布緊急采購,3分鐘左右您將得到回復。