- 您現在的位置:買賣IC網 > PDF目錄373970 > AD9875 (Analog Devices, Inc.) Broadband Modem Mixed-Signal Front End PDF資料下載

參數資料

| 型號: | AD9875 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Broadband Modem Mixed-Signal Front End |

| 中文描述: | 寬帶調制解調器混合信號前端 |

| 文件頁數: | 22/24頁 |

| 文件大小: | 288K |

| 代理商: | AD9875 |

REV. 0

AD9875

–22–

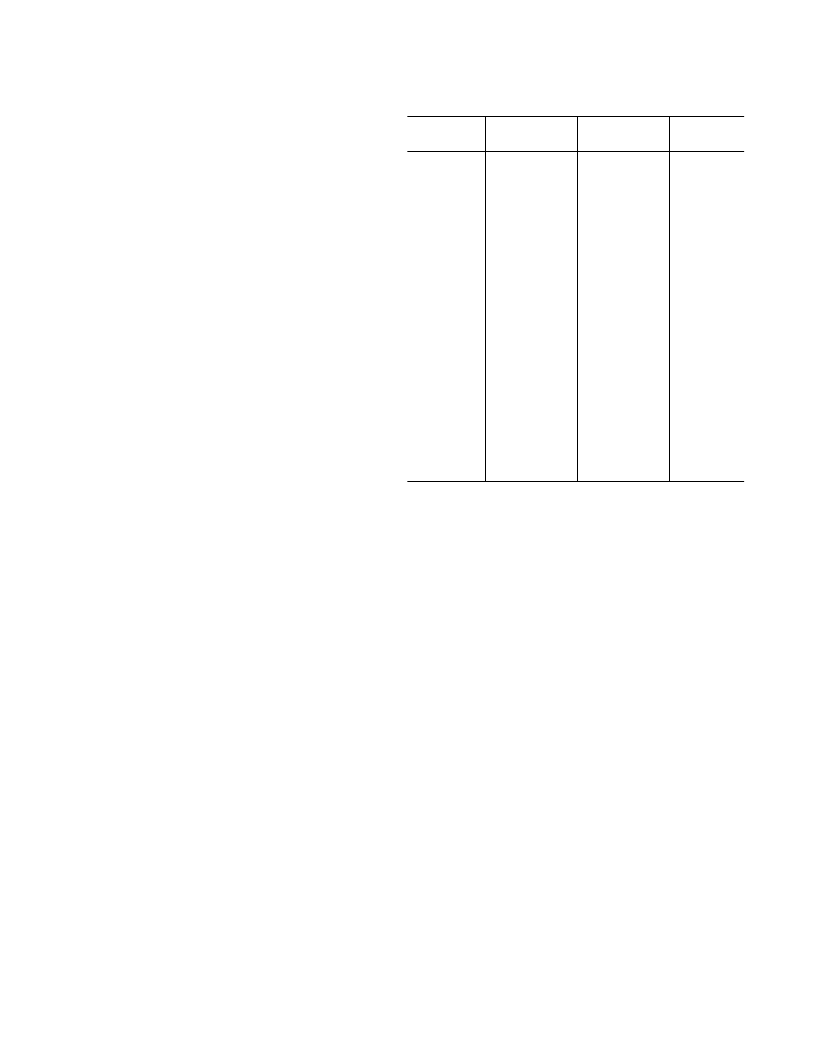

T able V. PGA Programming Map

Rx Path

Gain [4:0]

Rx Path

Gain

CPGA

Gain

SPGA

Gain

0

×

00

0

×

01

0

×

02

0

×

03

0

×

04

0

×

05

0

×

06

0

×

07

0

×

08

0

×

09

0

×

0A

0

×

0B

0

×

0C

0

×

0D

0

×

0E

0

×

0F

0

×

10

0

×

11

0

×

12

*

0

×

13

*

0

×

14

*

0

×

15

*

–6

–4

–2

0

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30/30

30/32

30/34

30/36

–6

–6

–6

–6

–6

–6

0

0

0

6

6

6

12

12

12

18

18

18

18/24

18/24

18/24

18/24

0

2

4

6

8

10

6

8

10

6

8

10

6

8

10

6

8

10

12/6

12/8

12/10

12/12

*

When the Wideband Rx Filter bit is set high, the Rx Path Gain is limited to

30 dB. T he first of the two values in the chart refers to this mode. T he second

number refers to the mode when the lower Rx LPF cutoff frequency is chosen,

or the Rx LPF filter is bypassed.

RE GIST E R 7—T RANSMIT PAT H SE T T INGS

T he AD9875 transmit path has a programmable interpolation

filter that precedes the transmit DAC. T he interpolation filter

can be programmed to operate in seven different modes. Also,

the digital interface can be programmed to operate in several

different modes. T hese modes are described below.

Bit 0: T ransmit Port Demultiplexer Bypass

Setting Bit 0 high bypasses the input data demultiplexer. In this

mode, consecutive nibbles on the T xDAT A(5:0) pins are treated

as individual words to be sent through the T x path. T his creates

a six bit data path. T he state of T xSYNC is ignored in this mode.

Bit 1: T ransmit Port Width

If Bit 1 is set high, the T x port will operate such that the most

significant nibble and the least significant nibble are each five

bits wide. T he default mode is six bits for the most significant

nibble and four bit for the least significant nibble. T he data is

always aligned to the MSB pin T x[5]. Enabling this pin on the

AD9875 allows for a five pin versus the default six pin interface.

Bit 2: T ransmit Port Least Significant Nibble First

Setting Bit 2 high reconfigures the AD 9875 for a transmit

mode that expects least significant nibble before the most

significant nibble.

Bit 2: Wideband Rx LPF

T his bit selects the nominal cutoff frequency of the 4-pole LPF.

Setting this bit high selects a nominal cutoff frequency of 28.8 MHz.

When the wideband filter is selected, the Rx path gain is limited

to 30 dB.

Bit 3: Fast ADC Sampling

Setting this bit increases the quiescent current in the SVGA

block. T his may provide some performance improvement

when the ADC sampling frequency is greater than 50 MSPS

(in 6-bit mode).

Bit 4: Rx Digital HPF Bypass

Setting this bit high bypasses the 1-pole digital HPF that follows

the ADC. T he digital filter must be bypassed for ADC sampling

above 50 MSPS.

Bit 5: Rx Path DC Offset Correction

Writing a One to this bit triggers an immediate receive path

offset correction and reads back zero after the completion of the

offset correction.

Bit 6: Rx LPF T uning Update In Progress

T his bit indicates when receive filter calibration is in progress.

T he duration of a receive filter calibration is about 500 ms.

Writing to this bit has no effect.

Bit 7: Rx LPF T uning Update Disable

Setting this bit high disables the automatic background receive

filter calibration. T he AD9875 automatically calibrates the

receive filter on reset and every few (~2) seconds thereafter to

compensate for process and temperature variation, power supply

and long term drift. Programming a one to this bit disables this

function. Programming a zero triggers an immediate first cali-

bration and enables the periodic update.

RE GIST E R 5—RE CE IVE FILT E R T UNING T ARGE T

T his register sets the filter tuning target as a function of f

OSCIN

.

See Register 4 description.

RE GIST E R 6—Rx PAT H GAIN ADJUST

T he AD9875 uses a combination of a continuous time PGA

(CPGA) and a switched capacitor PGA (SPGA) for a gain range

of –6 to 36 dB with a resolution of 2 dB. T he Rx path gain can

be programmed over the serial interface by writing to the Rx

Path Gain Adjust register or directly using the GAIN and MSB

aligned T x[5:1] bits. T he register default value is 0

×

00 for

lowest gain setting (–6 dB). T he register always reads back the

actual gain setting irrespective of which of the two programming

modes were used.

T able V describes the gains and how they are achieved as a

function of the Rx Path adjust bits.

Bit 5: PGA Gain Set through Register

Setting this bit high will result in the Rx Path Gain being set by

writing to the PGA Gain Control register. Default is zero which

selects writing the gain through the T x[5:1] pins in conjunction

with the gain pin.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9875-EB | Broadband Modem Mixed-Signal Front End |

| AD9875BST | Broadband Modem Mixed-Signal Front End |

| AD9876 | Broadband Modem Mixed-Signal Front End |

| AD9876-EB | Broadband Modem Mixed-Signal Front End |

| AD9876BST | Broadband Modem Mixed-Signal Front End |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9875BST | 制造商:Analog Devices 功能描述:Modem Chip Single 48-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:10B BROADBAND MODEM MXFE CONVERTER - Tape and Reel |

| AD9875BSTRL | 制造商:Analog Devices 功能描述:Modem Chip Single 48-Pin LQFP T/R |

| AD9875BSTZ | 制造商:Analog Devices 功能描述:Modem Chip Single 48-Pin LQFP |

| AD9875-EB | 制造商:Analog Devices 功能描述: |

| AD9876 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

發布緊急采購,3分鐘左右您將得到回復。