- 您現在的位置:買賣IC網 > PDF目錄374032 > ADSP-21160M (Analog Devices, Inc.) DSP Microcomputer PDF資料下載

參數資料

| 型號: | ADSP-21160M |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 數字信號處理 |

| 英文描述: | DSP Microcomputer |

| 中文描述: | DSP微機 |

| 文件頁數: | 10/53頁 |

| 文件大小: | 696K |

| 代理商: | ADSP-21160M |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

ADSP-21160M

–

10

–

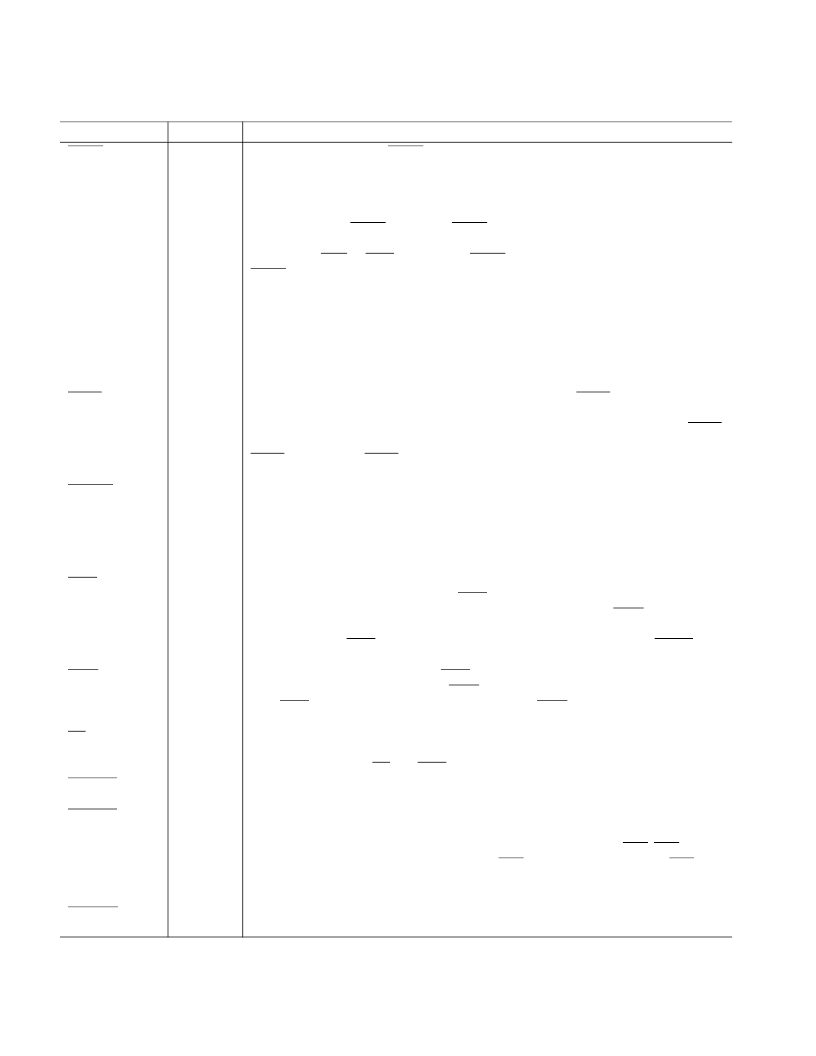

REV. 0

BRST

I/O/T

Sequential Burst Access. BRST is asserted by ADSP-21160M or a host to indicate that

data associated with consecutive addresses is being read or written. A slave device

samples the initial address and increments an internal address counter after each

transfer. The incremented address is not pipelined on the bus. If the burst access is a

read from host to ADSP-21160M, ADSP-21160M automatically increments the

address as long as BRST is asserted. BRST is asserted after the initial access of a burst

transfer. It is asserted for every cycle after that, except for the last data request cycle

(denoted by RDx or WRx asserted and BRST negated). A keeper latch on the DSP

’

s

BRST pin maintains the input at the level it was last driven (only enabled on the

ADSP-21160M with ID2

–

0 = 00x).

Memory Acknowledge. External devices can de-assert ACK (low) to add wait states to

an external memory access. ACK is used by I/O devices, memory controllers, or other

peripherals to hold off completion of an external memory access. The ADSP-21160M

deasserts ACK as an output to add wait states to a synchronous access of its internal

memory. A keeper latch on the DSP

’

s ACK pin maintains the input at the level it was

last driven (only enabled on the ADSP-21160M with ID2

–

0 = 00x).

Suspend Bus and Three-State. External devices can assert SBTS (low) to place the

external bus address, data, selects, and strobes in a high impedance state for the

following cycle. If the ADSP-21160M attempts to access external memory while SBTS

is asserted, the processor will halt and the memory access will not be completed until

SBTS is deasserted. SBTS should only be used to recover from host processor and/or

ADSP-21160M deadlock or used with a DRAM controller.

Interrupt Request Lines. These are sampled on the rising edge of CLKIN and may be

either edge-triggered or level-sensitive.

Flag Pins. Each is configured via control bits as either an input or output. As an input,

it can be tested as a condition. As an output, it can be used to signal external peripherals.

Timer Expired. Asserted for four CLKIN cycles when the timer is enabled and

TCOUNT decrements to zero.

Host Bus Request. Must be asserted by a host processor to request control of the

ADSP-21160M

’

s external bus. When HBR is asserted in a multiprocessing system, the

ADSP-21160M that is bus master will relinquish the bus and assert HBG. To relinquish

the bus, the ADSP-21160M places the address, data, select, and strobe lines in a high

impedance state. HBR has priority over all ADSP-21160M bus requests (BR6

–

1) in a

multiprocessing system.

Host Bus Grant. Acknowledges an HBR bus request, indicating that the host processor

may take control of the external bus. HBG is asserted (held low) by the ADSP-21160M

until HBR is released. In a multiprocessing system, HBG is output by the

ADSP-21160M bus master and is monitored by all others.

Chip Select. Asserted by host processor to select the ADSP-21160M.

Host Bus Acknowledge. The ADSP-21160M deasserts REDY (low) to add waitstates

to a host access when CS and HBR inputs are asserted.

DMA Request 1 (DMA Channel 11). Asserted by external port devices to request DMA

services.

DMA Request 2 (DMA Channel 12). Asserted by external port devices to request DMA

services.

Multiprocessing ID. Determines which multiprocessing bus request (BR1

–

BR6) is used

by ADSP-21160M. ID = 001 corresponds to BR1, ID = 010 corresponds to BR2, and

so on. Use ID = 000 or ID = 001 in single-processor systems. These lines are a system

configuration selection which should be hardwired or only changed at reset.

DMA Grant 1 (DMA Channel 11). Asserted by ADSP-21160M to indicate that the

requested DMA starts on the next cycle. Driven by bus master only.

ACK

I/O/S

SBTS

I/S

IRQ2

–

0

I/A

FLAG3

–

0

I/O/A

TIMEXP

O

HBR

I/A

HBG

I/O

CS

REDY

I/A

O (O/D)

DMAR1

I/A

DMAR2

I/A

ID2

–

0

I

DMAG1

O/T

Table 2. Pin Function Descriptions (Continued)

Pin

Type

Function

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-21160MKB-80 | DSP Microcomputer |

| ADSP-21160NKB-95 | DSP Microcomputer |

| ADSP-21160N | Cap-Free, NMOS, 150mA Low Dropout Regulator with Reverse Current Protection |

| ADSP-21160NCB-TBD | Cap-Free, NMOS, 150mA Low Dropout Regulator with Reverse Current Protection |

| ADSP-21161N | DSP Microcomputer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADSP-21160MKB-80 | 功能描述:IC DSP CONTROLLER 32BIT 400 BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21160MKBZ-80 | 功能描述:IC DSP CONTROLLER 32BIT 400 BGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21160N | 制造商:AD 制造商全稱:Analog Devices 功能描述:DSP Microcomputer |

| ADSP-21160NCB-100 | 功能描述:IC DSP CONTROLLER 32BIT 400BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21160NCB-TBD | 制造商:AD 制造商全稱:Analog Devices 功能描述:DSP Microcomputer |

發布緊急采購,3分鐘左右您將得到回復。