- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄374037 > ADSP-BF531 (Analog Devices, Inc.) Blackfin Embedded Processor PDF資料下載

參數(shù)資料

| 型號(hào): | ADSP-BF531 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | Blackfin Embedded Processor |

| 中文描述: | Blackfin嵌入式處理器 |

| 文件頁(yè)數(shù): | 6/56頁(yè) |

| 文件大小: | 671K |

| 代理商: | ADSP-BF531 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)

Rev. 0

|

Page 6 of 56

|

March 2004

ADSP-BF531/ADSP-BF532/ADSP-BF533

The asynchronous memory controller can be programmed to

control up to four banks of devices with very flexible timing

parameters for a wide variety of devices. Each bank occupies a

1M byte segment regardless of the size of the devices used, so

that these banks will only be contiguous if each is fully popu-

lated with 1M byte of memory.

I/O Memory Space

Blackfin processors do not define a separate I/O space. All

resources are mapped through the flat 32-bit address space.

On-chip I/O devices have their control registers mapped into

memory-mapped registers (MMRs) at addresses near the top of

the 4G byte address space. These are separated into two smaller

blocks, one of which contains the control MMRs for all core

functions, and the other of which contains the registers needed

for setup and control of the on-chip peripherals outside of the

core. The MMRs are accessible only in supervisor mode and

appear as reserved space to on-chip peripherals.

Booting

The ADSP-BF531/2/3 processor contains a small boot kernel,

which configures the appropriate peripheral for booting. If the

ADSP-BF531/2/3 processor is configured to boot from boot

ROM memory space, the processor starts executing from the

on-chip boot ROM. For more information, see

Booting Modes

on Page 13

.

Event Handling

The event controller on the ADSP-BF531/2/3 processor handles

all asynchronous and synchronous events to the processor. The

ADSP-BF531/2/3 processor provides event handling that sup-

ports both nesting and prioritization. Nesting allows multiple

event service routines to be active simultaneously. Prioritization

ensures that servicing of a higher priority event takes prece-

dence over servicing of a lower priority event. The controller

provides support for five different types of events:

Emulation – An emulation event causes the processor to

enter emulation mode, allowing command and control of

the processor via the JTAG interface.

Reset – This event resets the processor.

Non-Maskable Interrupt (NMI) – The NMI event can be

generated by the software watchdog timer or by the NMI

input signal to the processor. The NMI event is frequently

used as a power-down indicator to initiate an orderly shut-

down of the system.

Exceptions – Events that occur synchronously to program

flow (i.e., the exception will be taken before the instruction

is allowed to complete). Conditions such as data alignment

violations and undefined instructions cause exceptions.

Interrupts – Events that occur asynchronously to program

flow. They are caused by input pins, timers, and other

peripherals, as well as by an explicit software instruction.

Each event type has an associated register to hold the return

address and an associated return-from-event instruction. When

an event is triggered, the state of the processor is saved on the

supervisor stack.

The ADSP-BF531/2/3 processor Event Controller consists of

two stages, the Core Event Controller (CEC) and the System

Interrupt Controller (SIC). The Core Event Controller works

with the System Interrupt Controller to prioritize and control all

system events. Conceptually, interrupts from the peripherals

enter into the SIC, and are then routed directly into the general-

purpose interrupts of the CEC.

Core Event Controller (CEC)

The CEC supports nine general-purpose interrupts (IVG15–7),

in addition to the dedicated interrupt and exception events. Of

these general-purpose interrupts, the two lowest-priority inter-

rupts (IVG15–14) are recommended to be reserved for software

interrupt handlers, leaving seven prioritized interrupt inputs to

support the peripherals of the ADSP-BF531/2/3 processor.

Table 2

describes the inputs to the CEC, identifies their names

in the Event Vector Table (EVT), and lists their priorities.

System Interrupt Controller (SIC)

The System Interrupt Controller provides the mapping and

routing of events from the many peripheral interrupt sources to

the prioritized general-purpose interrupt inputs of the CEC.

Although the ADSP-BF531/2/3 processor provides a default

mapping, the user can alter the mappings and priorities of

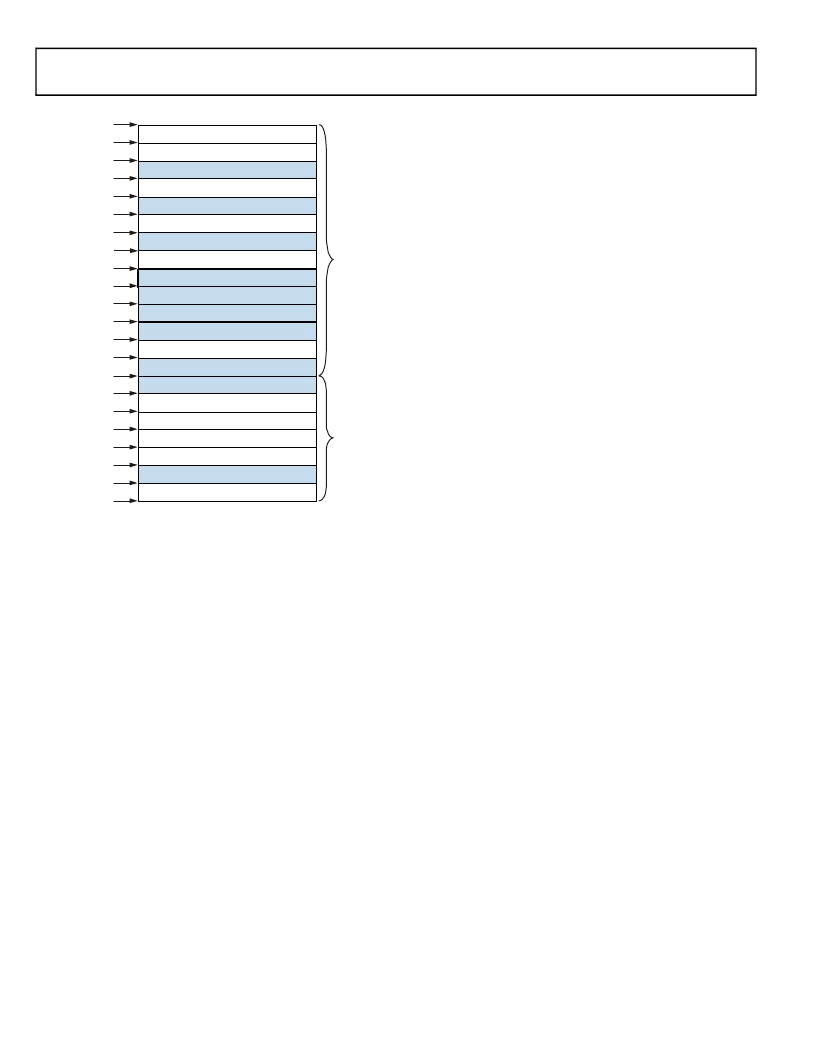

Figure 5. ADSP-BF531 Internal/External Memory Map

CORE MMR REGISTERS (2M BYTE)

RESERVED

SCRATCHPAD SRAM (4K BYTE)

SYSTEM MMR REGISTERS (2M BYTE)

RESERVED

RESERVED

RESERVED

DATA BANK A SRAM / CACHE (16K BYTE)

ASYNC MEMORY BANK 3 (1M BYTE)

ASYNC MEMORY BANK 2 (1M BYTE)

ASYNC MEMORY BANK 1 (1M BYTE)

ASYNC MEMORY BANK 0 (1M BYTE)

SDRAM MEMORY (16M BYTE TO 128M BYTE)

INSTRUCTION SRAM / CACHE (16K BYTE)

I

E

0xFFFF FFFF

0xFFE0 0000

0xFFB0 0000

0xFFA1 4000

0xFFA0 8000

0xFF90 8000

0xFF90 4000

0xFF80 8000

0xFF80 4000

0xEF00 0000

0x2040 0000

0x2030 0000

0x2020 0000

0x2010 0000

0x2000 0000

0x0800 0000

0x0000 0000

0xFFC0 0000

0xFFB0 1000

0xFFA0 0000

RESERVED

RESERVED

RESERVED

0xFFA1 0000

INSTRUCTION SRAM (16K BYTE)

RESERVED

RESERVED

0xFFA0 C000

RESERVED

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADSP-BF531SBBC400 | Metal Connector Backshell |

| ADSP-BF531SBBZ400 | Blackfin Embedded Processor |

| ADSP-BF531SBST400 | Circular Connector Series:97 |

| ADSP-BF532 | Blackfin Embedded Processor |

| ADSP-BF532SBBC400 | Blackfin Embedded Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-BF531SBB400 | 功能描述:IC DSP CTLR 16BIT 400MHZ 169-BGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數(shù)字式信號(hào)處理器) 系列:Blackfin® 標(biāo)準(zhǔn)包裝:2 系列:StarCore 類型:SC140 內(nèi)核 接口:DSI,以太網(wǎng),RS-232 時(shí)鐘速率:400MHz 非易失內(nèi)存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,F(xiàn)CBGA 供應(yīng)商設(shè)備封裝:431-FCPBGA(20x20) 包裝:托盤(pán) |

| ADSPBF531SBBC400 | 制造商:Analog Devices 功能描述: |

| ADSP-BF531SBBC400 | 功能描述:IC DSP CTLR 16B 400MHZ 160MBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - DSP(數(shù)字式信號(hào)處理器) 系列:Blackfin® 標(biāo)準(zhǔn)包裝:2 系列:StarCore 類型:SC140 內(nèi)核 接口:DSI,以太網(wǎng),RS-232 時(shí)鐘速率:400MHz 非易失內(nèi)存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,F(xiàn)CBGA 供應(yīng)商設(shè)備封裝:431-FCPBGA(20x20) 包裝:托盤(pán) |

| ADSP-BF531SBBC-400X | 制造商:Analog Devices 功能描述: |

| ADSP-BF531SBBC-ENG | 制造商:Analog Devices 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。