- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄374037 > ADSP-BF531 (Analog Devices, Inc.) Blackfin Embedded Processor PDF資料下載

參數(shù)資料

| 型號(hào): | ADSP-BF531 |

| 廠商: | Analog Devices, Inc. |

| 元件分類(lèi): | 數(shù)字信號(hào)處理 |

| 英文描述: | Blackfin Embedded Processor |

| 中文描述: | Blackfin嵌入式處理器 |

| 文件頁(yè)數(shù): | 7/56頁(yè) |

| 文件大小: | 671K |

| 代理商: | ADSP-BF531 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)

ADSP-BF531/ADSP-BF532/ADSP-BF533

Rev. 0

|

Page 7 of 56

|

March 2004

interrupt events by writing the appropriate values into the Inter-

rupt Assignment Registers (IAR).

Table 3

describes the inputs

into the SIC and the default mappings into the CEC.

Event Control

The ADSP-BF531/2/3 processor provides the user with a very

flexible mechanism to control the processing of events. In the

CEC, three registers are used to coordinate and control events.

Each register is 16 bits wide:

CEC Interrupt Latch Register (ILAT) – The ILAT register

indicates when events have been latched. The appropriate

bit is set when the processor has latched the event and

cleared when the event has been accepted into the system.

This register is updated automatically by the controller, but

it may be written only when its corresponding IMASK bit

is cleared.

CEC Interrupt Mask Register (IMASK) – The IMASK reg-

ister controls the masking and unmasking of individual

events. When a bit is set in the IMASK register, that event is

unmasked and will be processed by the CEC when asserted.

A cleared bit in the IMASK register masks the event, pre-

venting the processor from servicing the event even though

the event may be latched in the ILAT register. This register

may be read or written while in supervisor mode. (Note

that general-purpose interrupts can be globally enabled and

disabled with the STI and CLI instructions, respectively.)

CEC Interrupt Pending Register (IPEND) – The IPEND

register keeps track of all nested events. A set bit in the

IPEND register indicates the event is currently active or

nested at some level. This register is updated automatically

by the controller but may be read while in supervisor mode.

The SIC allows further control of event processing by providing

three 32-bit interrupt control and status registers. Each register

contains a bit corresponding to each of the peripheral interrupt

events shown in

Table 3 on Page 7

.

SIC Interrupt Mask Register (SIC_IMASK)– This register

controls the masking and unmasking of each peripheral

interrupt event. When a bit is set in the register, that

peripheral event is unmasked and will be processed by the

system when asserted. A cleared bit in the register masks

the peripheral event, preventing the processor from servic-

ing the event.

SIC Interrupt Status Register (SIC_ISR) – As multiple

peripherals can be mapped to a single event, this register

allows the software to determine which peripheral event

source triggered the interrupt. A set bit indicates the

peripheral is asserting the interrupt, and a cleared bit indi-

cates the peripheral is not asserting the event.

SIC Interrupt Wakeup Enable Register (SIC_IWR) – By

enabling the corresponding bit in this register, a peripheral

can be configured to wake up the processor, should the

core be idled when the event is generated. (

For more infor-

mation, see Dynamic Power Management on Page 11.

)

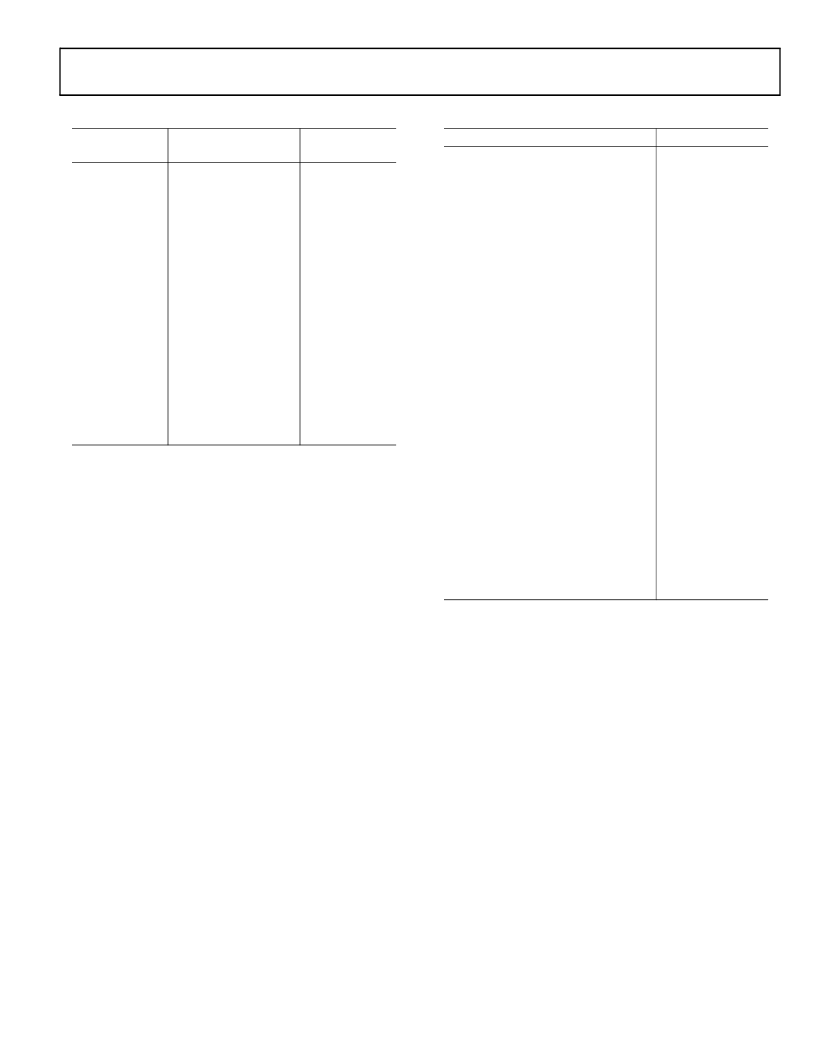

Table 2. Core Event Controller (CEC)

Priority

(0 is Highest)

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Event Class

EVT Entry

Emulation/Test Control

Reset

Non-Maskable Interrupt

Exception

Reserved

Hardware Error

Core Timer

General Interrupt 7

General Interrupt 8

General Interrupt 9

General Interrupt 10

General Interrupt 11

General Interrupt 12

General Interrupt 13

General Interrupt 14

General Interrupt 15

EMU

RST

NMI

EVX

IVHW

IVTMR

IVG7

IVG8

IVG9

IVG10

IVG11

IVG12

IVG13

IVG14

IVG15

Table 3. System Interrupt Controller (SIC)

Peripheral Interrupt Event

PLL Wakeup

DMA Error

PPI Error

SPORT 0 Error

SPORT 1 Error

SPI Error

UART Error

Real-Time Clock

DMA Channel 0 (PPI)

DMA Channel 1 (SPORT 0 RX)

DMA Channel 2 (SPORT 0 TX)

DMA Channel 3 (SPORT 1 RX)

DMA Channel 4 (SPORT 1 TX)

DMA Channel 5 (SPI)

DMA Channel 6 (UART RX)

DMA Channel 7 (UART TX)

Timer 0

Timer 1

Timer 2

PF Interrupt A

PF Interrupt B

DMA Channels 8 and 9

(Memory DMA Stream 1)

DMA Channels 10 and 11

(Memory DMA Stream 0)

Software Watchdog Timer

Default Mapping

IVG7

IVG7

IVG7

IVG7

IVG7

IVG7

IVG7

IVG8

IVG8

IVG9

IVG9

IVG9

IVG9

IVG10

IVG10

IVG10

IVG11

IVG11

IVG11

IVG12

IVG12

IVG13

IVG13

IVG13

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADSP-BF531SBBC400 | Metal Connector Backshell |

| ADSP-BF531SBBZ400 | Blackfin Embedded Processor |

| ADSP-BF531SBST400 | Circular Connector Series:97 |

| ADSP-BF532 | Blackfin Embedded Processor |

| ADSP-BF532SBBC400 | Blackfin Embedded Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-BF531SBB400 | 功能描述:IC DSP CTLR 16BIT 400MHZ 169-BGA RoHS:是 類(lèi)別:集成電路 (IC) >> 嵌入式 - DSP(數(shù)字式信號(hào)處理器) 系列:Blackfin® 標(biāo)準(zhǔn)包裝:2 系列:StarCore 類(lèi)型:SC140 內(nèi)核 接口:DSI,以太網(wǎng),RS-232 時(shí)鐘速率:400MHz 非易失內(nèi)存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類(lèi)型:表面貼裝 封裝/外殼:431-BFBGA,F(xiàn)CBGA 供應(yīng)商設(shè)備封裝:431-FCPBGA(20x20) 包裝:托盤(pán) |

| ADSPBF531SBBC400 | 制造商:Analog Devices 功能描述: |

| ADSP-BF531SBBC400 | 功能描述:IC DSP CTLR 16B 400MHZ 160MBGA RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - DSP(數(shù)字式信號(hào)處理器) 系列:Blackfin® 標(biāo)準(zhǔn)包裝:2 系列:StarCore 類(lèi)型:SC140 內(nèi)核 接口:DSI,以太網(wǎng),RS-232 時(shí)鐘速率:400MHz 非易失內(nèi)存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類(lèi)型:表面貼裝 封裝/外殼:431-BFBGA,F(xiàn)CBGA 供應(yīng)商設(shè)備封裝:431-FCPBGA(20x20) 包裝:托盤(pán) |

| ADSP-BF531SBBC-400X | 制造商:Analog Devices 功能描述: |

| ADSP-BF531SBBC-ENG | 制造商:Analog Devices 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。