- 您現在的位置:買賣IC網 > PDF目錄374047 > ADV7344BSTZ (ANALOG DEVICES INC) Multiformat Video Encoder Six 14-Bit Noise Shaped Video DACs PDF資料下載

參數資料

| 型號: | ADV7344BSTZ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | DAC |

| 英文描述: | Multiformat Video Encoder Six 14-Bit Noise Shaped Video DACs |

| 中文描述: | SERIAL INPUT LOADING, 14-BIT DAC, PQFP64 |

| 封裝: | ROHS COMPLIANT, MS-026BCD, LQFP-64 |

| 文件頁數: | 18/88頁 |

| 文件大小: | 1078K |

| 代理商: | ADV7344BSTZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁

ADV7344

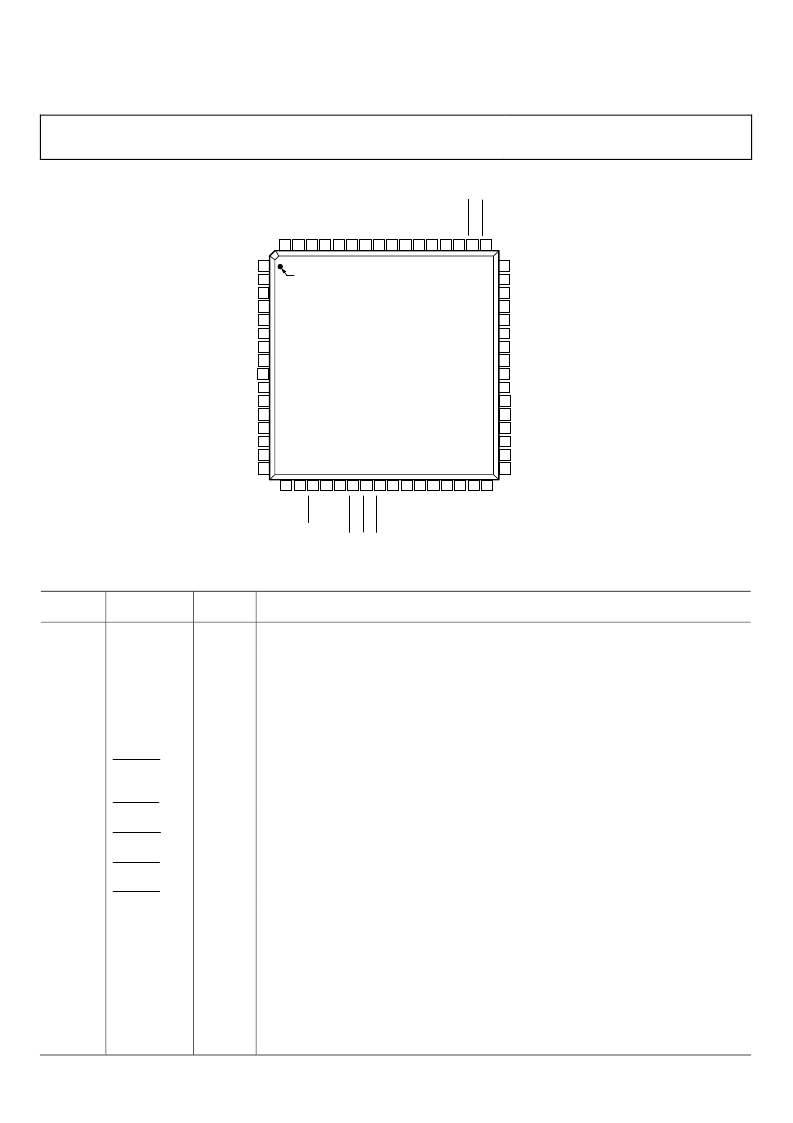

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Rev. 0 | Page 18 of 88

64

G

63

C

62

S

61

S

60

S

59

S

58

S

57

D

56

V

D

55

S

54

S

53

S

52

S

51

S

50

S

49

S

47

R

SET1

46

V

REF

45

COMP1

42

DAC 3

43

DAC 2

44

DAC 1

48

SFL/MISO

41

V

AA

40

AGND

39

DAC 4

37

DAC 6

36

R

SET2

35

COMP2

34

PV

DD

33

EXT_LF1

38

DAC 5

2

Y0

3

Y1

4

Y2

7

Y5

6

Y4

5

Y3

1

V

DD_IO

8

Y6

9

Y7

10

V

DD

12

Y8

13

Y9

14

C0

15

C1

16

C2

11

DGND

17

C

18

C

19

A

20

S

21

S

22 23

P

24

P

25

P

26

C

C

27

C

28

C

29

C

30

C

31

32

P

PIN 1

ADV7344

TOP VIEW

(Not to Scale)

E

0

Figure 21. Pin Configuration

Table 13. Pin Function Descriptions

Pin No.

13, 12,

9 to 2

29 to 25,

18 to 14

62 to 58,

55 to 51

30

63

Mnemonic

Y9 to Y0

Input/

Output

I

Description

10-Bit Pixel Port (Y9 to Y0). Y0 is the LSB. Refer to Table 31 for input modes.

C9 to C0

I

10-Bit Pixel Port (C9 to C0). C0 is the LSB. Refer to Table 31 for input modes.

S9 to S0

I

10-Bit Pixel Port (S9 to S0). S0 is the LSB. Refer to Table 31 for input modes.

CLKIN_A

CLKIN_B

I

I

Pixel Clock Input for HD only (74.25 MHz), ED

1

only (27 MHz or 54 MHz) or SD only (27 MHz).

Pixel Clock Input for Dual Modes Only. Requires a 27 MHz reference clock for ED operation or a

74.25 MHz reference clock for HD operation.

SD Horizontal Synchronization Signal. This pin can also be configured to output an SD, ED, or HD

horizontal synchronization signal. See the External Horizontal and Vertical Synchronization

Control section.

SD Vertical Synchronization Signal. This pin can also be configured to output an SD, ED, or HD vertical

synchronization signal. See the External Horizontal and Vertical Synchronization Control section.

ED/HD Horizontal Synchronization Signal. See the External Horizontal and Vertical

Synchronization Control section.

ED/HD Vertical Synchronization Signal. See the External Horizontal and Vertical Synchronization

Control section.

ED/HD Blanking Signal. See the External Horizontal and Vertical Synchronization Control section.

Multifunctional Pin: Subcarrier Frequency Lock (SFL) Input/SPI Data Output. The SFL input is

used to drive the color subcarrier DDS system, timing reset, or subcarrier reset.

This pin is used to control the amplitudes of the DAC 1, DAC 2, and DAC 3 outputs. For full-drive

operation (for example, into a 37.5 Ω load), a 510 Ω resistor must be connected from R

SET1

to

AGND. For low drive operation (for example, into a 300 Ω load), a 4.12 kΩ resistor must be

connected from R

SET1

to AGND.

This pin is used to control the amplitudes of the DAC 4, DAC 5, and DAC 6 outputs. A 4.12 kΩ

resistor must be connected from R

SET2

to AGND.

Compensation Pins. Connect a 2.2 nF capacitor from both COMP pins to V

AA

.

50

S_HSYNC

I/O

49

S_VSYNC

I/O

22

P_HSYNC

I

23

P_VSYNC

I

24

48

P_BLANK

SFL/MISO

I

I/O

47

R

SET1

I

36

R

SET2

I

45, 35

COMP1,

COMP2

O

相關PDF資料 |

PDF描述 |

|---|---|

| ADV7390 | Low Power, Chip Scale 10-Bit SD/HD Video Encoder |

| ADV7390BCPZ | Low Power, Chip Scale 10-Bit SD/HD Video Encoder |

| ADV7390BCPZ-REEL | Low Power, Chip Scale 10-Bit SD/HD Video Encoder |

| ADV7390EBZ | Low Power, Chip Scale 10-Bit SD/HD Video Encoder |

| ADV7391 | Low Power, Chip Scale 10-Bit SD/HD Video Encoder |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADV73505501 | 制造商:LG Corporation 功能描述:Frame Assembly |

| ADV73506801 | 制造商:LG Corporation 功能描述:Frame Assembly |

| ADV73625610 | 制造商:LG Corporation 功能描述:Frame Assembly |

| ADV73625613 | 制造商:LG Corporation 功能描述:Frame Assembly |

| ADV73625616 | 制造商:LG Corporation 功能描述:Frame Assembly |

發布緊急采購,3分鐘左右您將得到回復。