- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98215 > TFP9431CPAP (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP64 PDF資料下載

參數(shù)資料

| 型號: | TFP9431CPAP |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| 封裝: | 10 X 10 MM, 1.40 MM HEIGHT, 0.50 MM PITCH, POWER, THERMALLY ENHANCED, PLASTIC, TQFP-64 |

| 文件頁數(shù): | 6/18頁 |

| 文件大小: | 241K |

| 代理商: | TFP9431CPAP |

TFP9431

PanelBus

DVI RECEIVER WITH TRIPLE DAC

SLDS122A – MARCH 2000 – REVISED JUNE 2000

14

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

detailed description (continued)

TFP9431 incorporates HSYNC jitter immunity

Several DVI transmitters available in the market introduce jitter on the transmitted HSYNC and VSYNC signals

during the TMDS encryption process. The HSYNC signal can shift by one pixel position (one clock) from nominal

in either direction, resulting in up to two cycles of HSYNC shift. This jitter carries through to the DVI receiver,

and if the position of HSYNC shifts continuously, the receiver can lose track of the input timing and pixel noise

will occur on the display. This jitter problem has been shown to be extremely visible on 1280 x 1024 at 85 Hz

CRT monitors and other DVI displays. For this reason, a DVI compliant receiver with HSYNC jitter immunity

should be used in all displays that could be connected to host PCs with transmitters that have this HSYNC jitter

problem.

The TFP9431 integrates HSYNC regeneration circuitry that provides a seamless interface to these

noncompliant transmitters. The position of the data enable (DE) signal is always fixed in relation to data,

irrespective of the location of HSYNC. The TFP9431 receiver uses the DE and clock signals recreate stable

vertical and horizontal sync signals. The circuit filters the HSYNC output of the receiver, and HSYNC is shifted

to the nearest eighth bit boundary, producing a stable output with respect to data, as shown in Figure 16. This

will ensure accurate data synchronization at the input of the display timing controller.

This HSYNC regeneration circuit is transparent to the monitor and need not be removed even if the transmitted

HSYNC is stable. For example, the PanelBus

line of DVI 1.0 compliant transmitters, such as the TFP6422

and TFP420, do not have the HSYNC jitter problem. The TFP9431 will operate correctly with either compliant

or noncompliant transmitters.

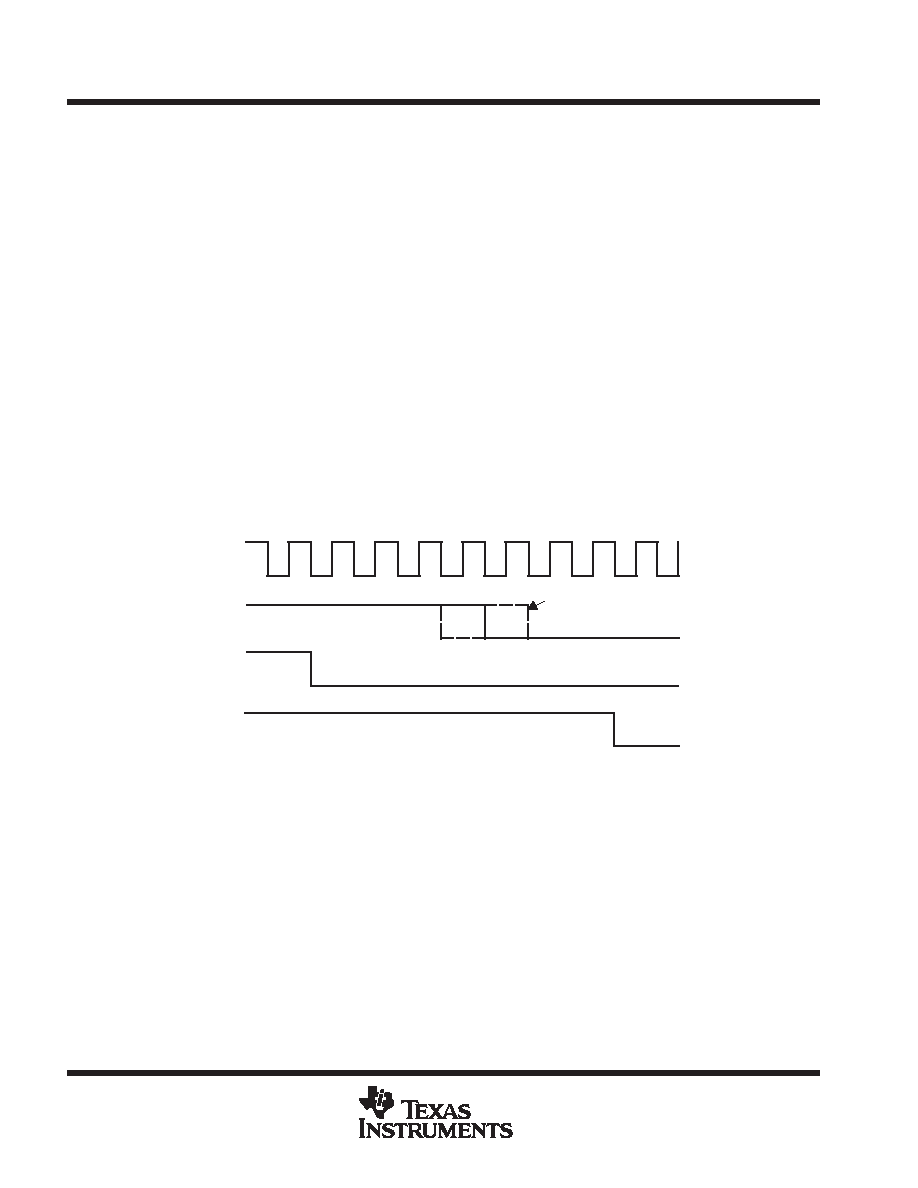

HSYNC Shift by

± 1 Clock

ODCK

HSYNC IN

DE

HSYNC OUT

Figure 16. HSYNC Regeneration Timing Diagram

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TG355ENK-7916 | 8.15 MHz, LOW PASS FILTER |

| TH355BDI-4957 | 4.43 MHz, BAND PASS FILTER |

| TH355LDK-7915 | 8.15 MHz, LOW PASS FILTER |

| TH355LNK-4550 | 10 MHz, LOW PASS FILTER |

| TH355LNK-4867 | 5 MHz, LOW PASS FILTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TFP-AA-10T-13 | 制造商:DIALIGHT 制造商全稱:Dialight Corporation 功能描述:Tactical Composite Front Park Turn Light |

| TFPAA13B13 | 制造商:Dialight 功能描述: |

| TFPAA13D13 | 制造商:Dialight 功能描述: |

| TFPAA13T13 | 制造商:Dialight 功能描述: |

| TFP-AA-13T-13 | 制造商:DIALIGHT 制造商全稱:Dialight Corporation 功能描述:Tactical Composite Front Park Turn Light |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。