- 您現在的位置:買賣IC網 > PDF目錄98229 > THS8210PFP (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP80 PDF資料下載

參數資料

| 型號: | THS8210PFP |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| 封裝: | POWER, PLASTIC, TQFP-80 |

| 文件頁數: | 7/73頁 |

| 文件大小: | 2053K |

| 代理商: | THS8210PFP |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

THS8200/8210

‘ALL-FORMAT’ OVERSAMPLED COMPONENT VIDEO/PC GRAPHICS D/A SYSTEM WITH

THREE 11 BIT DAC’S, CGMS DATA INSERTION AND 525P MACROVISION

TM COPY

PROTECTION

SLES032—6/18/02 3:33 PM

POST OFFICE BOX 655303

DALLAS TEXAS 77265

15

Copyright 2001 Texas Instruments Incorporated

PRODUCT PREVIEW information concerns products in the

formative or design phase of development. Characteristic data

and other specifications are design goals. Texas Instruments

reserves the right to change or discontinue these products

without notice.

Detailed Functional Description

Data manager (DMAN)

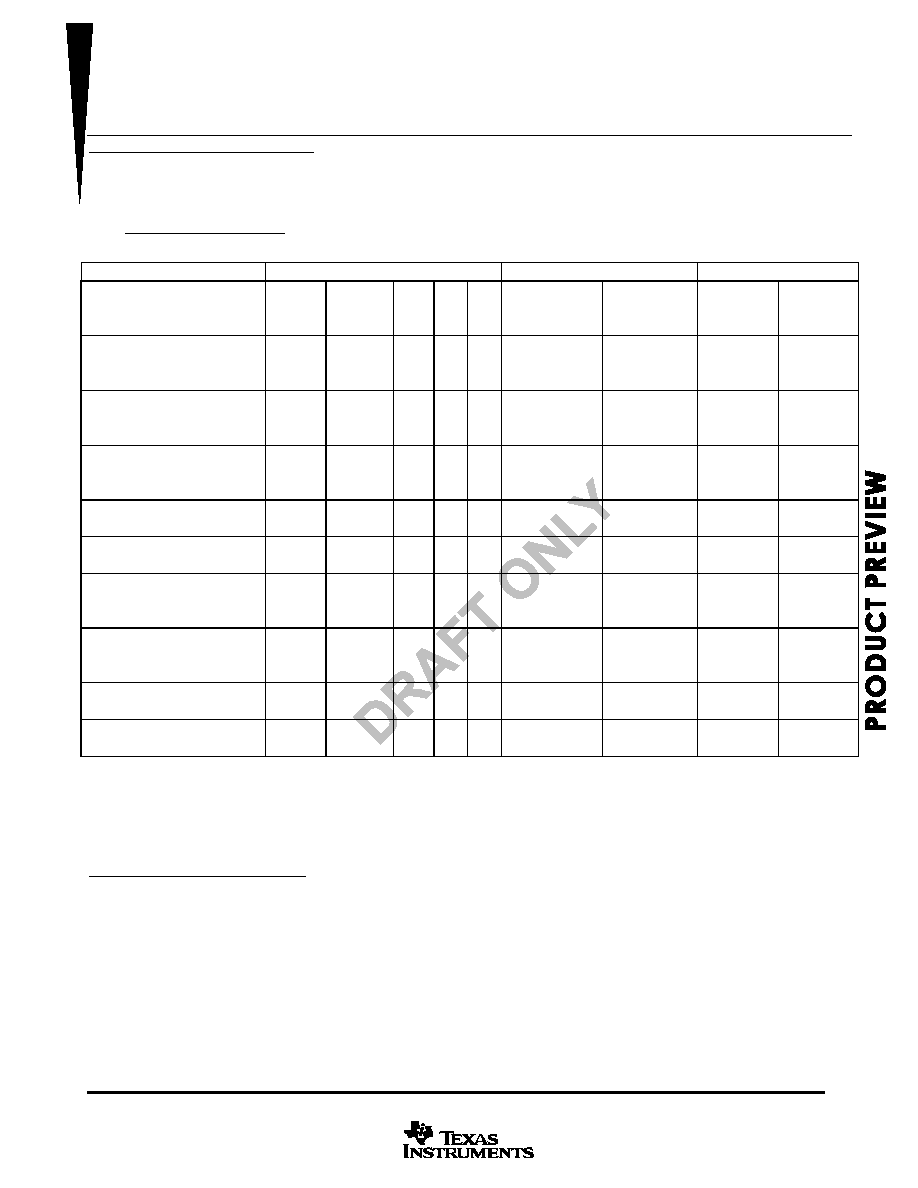

Supported input formats

INPUT INTERFACE

TIMING CONTROL

SYNCHRONIZATION

30 bit

20 bit

10

bit

2

16

bit

15

bit

Embedded

timing

Dedicated

timing

Master

Slave

[PRESET]

HDTV

–

SMPTE296M

progressive (720P)

X

(4:4:4)

X

(4:2:2)

X

[PRESET]

HDTV

–

SMPTE274M

progressive (1080P)

X

(4:4:4)

X

(4:2:2)

X

[PRESET]

HDTV

–

SMPTE274M

interlaced (1080I)

X

(4:4:4)

X

(4:2:2)

X

[GENERIC]

HDTV

X

(4:4:4)

X

(4:2:2)

X

[PRESET]

SDTV-ITU.1358 (525P)

X

3

X

[PRESET]

SDTV

–

ITU-R.BT470

(525I)

X

4

X

[PRESET]

SDTV-ITU-R.BT470

(625I )

X

5

X

[GENERIC]

SDTV

X

(4:4:4)

X

(4:2:2)

X

[PRESET]

VESA

X

6

X

7

X

8

X

2 The ITU-R.BT656 output bus on THS8200 can be enabled via an I2C register bit when the device is configured to

receive data over a 10bit input interface, to send this data to an external device. In other DMAN modes, this output

should remain off (register ‘data_tristate656’)

3 SMPTE293M-compliant

4 ITU.R-BT656 compliant

5 ITU-R.BT656 compliant

6 since PC graphics data is normally only 8 bit wide, only 3x8 bit (8MSB’s of each bus) will be used. Color space

converter bypass required for modes with pixelclock > 150MSPS.

7 see footnote for 30-bit VESA format

8 see footnote for 30-bit VESA format

相關PDF資料 |

PDF描述 |

|---|---|

| TK10840MCBX | FM, AUDIO DEMODULATOR, PDSO20 |

| TK10840MCMG | FM, AUDIO DEMODULATOR, PDSO20 |

| TK10840MCTL | FM, AUDIO DEMODULATOR, PDSO20 |

| TK10840MCTR | FM, AUDIO DEMODULATOR, PDSO20 |

| TK10840MCTX | FM, AUDIO DEMODULATOR, PDSO20 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| THS8-38R-D | 制造商:Thomas & Betts 功能描述:HEAT SHRINK RING 8AWG 3/8 STUD 制造商:Thomas & Betts 功能描述:CATAMOUNT CABLE TIES |

| THS8-516R-D | 制造商:Thomas & Betts 功能描述:CATAMOUNT CABLE TIES |

| THS8-BS-W | 制造商:Thomas & Betts 功能描述:HEAT SHRINK BUTT SPLICE 8AWG |

| THS9 | 制造商:Apex Tool Group 功能描述:HS-9 9/32 HEX NUTDRIVER |

| THS9000 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:50 MHz to 400 MHz CASCADEABLE AMPLIFIER |

發布緊急采購,3分鐘左右您將得到回復。