- 您現在的位置:買賣IC網 > PDF目錄98252 > TLV320ADC3001IYZHT (TEXAS INSTRUMENTS INC) 2-CH 16-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, PBGA16 PDF資料下載

參數資料

| 型號: | TLV320ADC3001IYZHT |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 2-CH 16-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, PBGA16 |

| 封裝: | GREEN, DSBGA-16 |

| 文件頁數: | 15/81頁 |

| 文件大小: | 836K |

| 代理商: | TLV320ADC3001IYZHT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁

LD(n)

LD (n+1)

2

1

0

3

0

3

2

1

3

RD(n)

LEFT CHANNEL

RIGHT CHANNEL

WORD

CLOCK

BIT

CLOCK

DATA

n-1 n-2 n-3

Ch_Offset_1 = 0

RD(n)

RD(n+1)

2

1

0

3

0

3

2

1

3

LD(n)

RIGHT CHANNEL

LEFT CHANNEL

WORD

CLOCK

BIT

CLOCK

DATA

n-1 n-2 n-3

Ch_Offset_1 = 0

Ch_Offset_2 = 3

RD(n)

RD(n+1)

2

1

0

3

0

3

2

1

3

LD(n)

RIGHT CHANNEL

LEFT CHANNEL

WORD

CLOCK

BIT

CLOCK

DATA

n-1 n-2 n-3

Ch_Offset_1 = 0

Ch_Offset_2 = 3

SLAS548C

– OCTOBER 2008 – REVISED APRIL 2011

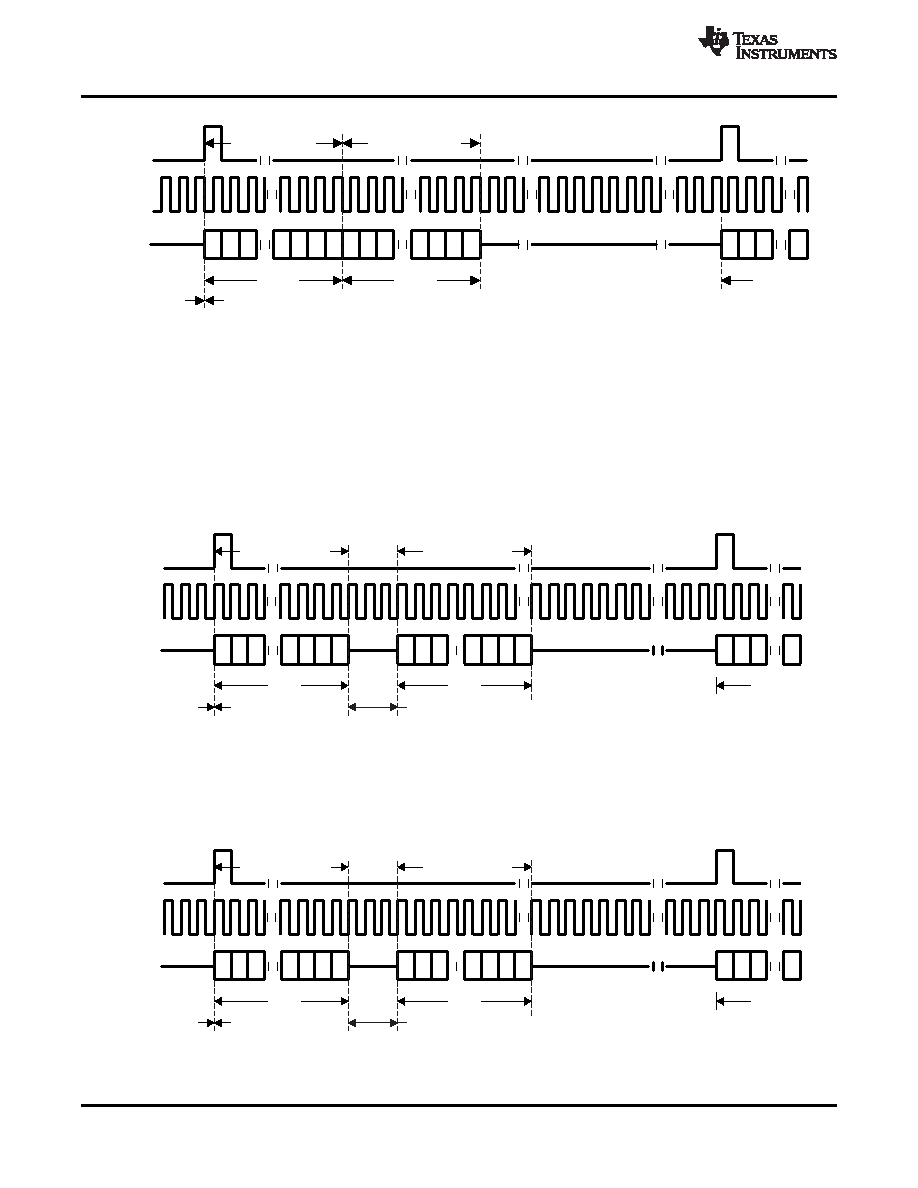

Figure 28. DSP Mode With Ch_Offset_1 = 0, Bit Clock Inverted

For DSP mode, the number of bit clocks per frame should be greater than twice the programmed word length of

the data. Also, the programmed offset value should be less than the number of bit clocks per frame by at least

the programmed word length of the data.

Figure 29 shows the DSP time-slot-based mode without channel swapping, and with Ch_Offset_1 = 0 and

Ch_Offset_2 = 3. The MSB of left channel data is valid on the first falling edge of the bit clock after the rising

edge of the word clock. Because the right channel has an offset of 3, the MSB of its data is valid on the third

falling edge of the bit clock after the LSB of the left-channel data. As in the case of other modes, the serial output

bus is put in the high-impedance state, if Hi-Z state operation of the output is enabled, during all the extra

bit-clock cycles in the frame.

Figure 29. DSP Mode, Time-Slot-Based Mode Enabled, Ch_Offset_1 = 0, Ch_Offset_2 = 3

Figure 30 shows the timing diagram for the DSP mode with left and right channels swapped, Ch_Offset_1 = 0,

and Ch_Offset_2 = 3. The MSB of the right channel is valid on the first falling edge of the bit clock after the rising

edge of the word clock. And, the MSB of the left channel is valid three bit-clock cycles after the LSB of right

channel, because the offset for the left channel is 3.

Figure 30. DSP Mode, Time-Slot-Based Mode Enabled, Ch_Offset_1 = 0, Ch_Offset_2 = 3, Channel Swap

Enabled

22

Copyright

2008–2011, Texas Instruments Incorporated

相關PDF資料 |

PDF描述 |

|---|---|

| TLV320ADC3001IYZHR | 2-CH 16-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, PBGA16 |

| TLV320ADC3101IRGER320 | SPECIALTY CONSUMER CIRCUIT, PQCC24 |

| TLV320ADC3101IRGET320 | SPECIALTY CONSUMER CIRCUIT, PQCC24 |

| TLV320ADC3101IRGER | SPECIALTY CONSUMER CIRCUIT, PQCC24 |

| TLV320ADC3101IRGET | SPECIALTY CONSUMER CIRCUIT, PQCC24 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TLV320ADC3001IYZHT | 制造商:Texas Instruments 功能描述:Analog/Digital (A/D) Converter IC |

| TLV320ADC3101 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Low Power Stereo ADC for Wireless Handsets and Portable Audio |

| TLV320ADC3101EVM-K | 功能描述:音頻 IC 開發工具 TLV320ADC3101EVM-K Eval Mod RoHS:否 制造商:Texas Instruments 產品:Evaluation Kits 類型:Audio Amplifiers 工具用于評估:TAS5614L 工作電源電壓:12 V to 38 V |

| TLV320ADC3101IRGER | 功能描述:音頻模/數轉換器 IC 92dB (16B) Low Power Stereo ADC RoHS:否 制造商:Wolfson Microelectronics 轉換速率: 分辨率: ADC 輸入端數量: 工作電源電壓: 最大工作溫度: 最小工作溫度: 安裝風格: 封裝 / 箱體: 封裝: |

| TLV320ADC3101IRGET | 功能描述:音頻模/數轉換器 IC 92dB (16B) Low Power Stereo ADC RoHS:否 制造商:Wolfson Microelectronics 轉換速率: 分辨率: ADC 輸入端數量: 工作電源電壓: 最大工作溫度: 最小工作溫度: 安裝風格: 封裝 / 箱體: 封裝: |

發布緊急采購,3分鐘左右您將得到回復。