- 您現在的位置:買賣IC網 > PDF目錄98255 > TLV320DAC32IRHBT (TEXAS INSTRUMENTS INC) SERIAL INPUT LOADING, DAC WITH PROGRAMMABLE PLL, PQCC32 PDF資料下載

參數資料

| 型號: | TLV320DAC32IRHBT |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | DAC |

| 英文描述: | SERIAL INPUT LOADING, DAC WITH PROGRAMMABLE PLL, PQCC32 |

| 封裝: | 5 X 5 MM, GREEN, PLASTIC, QFN-32 |

| 文件頁數: | 11/69頁 |

| 文件大小: | 1242K |

| 代理商: | TLV320DAC32IRHBT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁

OVERVIEW

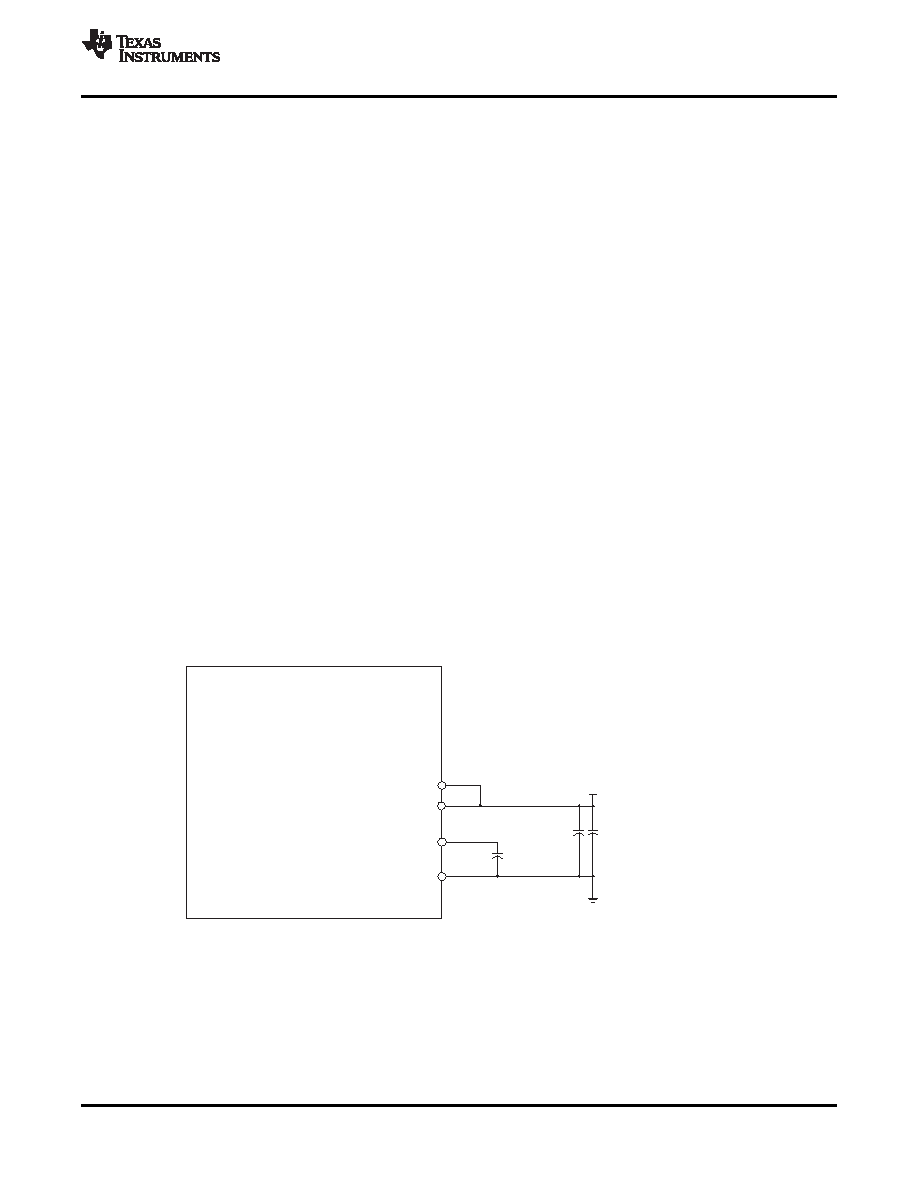

LDO OPERATION

LDO=ON

TLV320DAC32

IOVDD

D

IOVDD

3.3V

1 F

m

0.1 F

m

DVDD

IOVSS

LDO_SELECT

0.1 F

m

www.ti.com........................................................................................................................................ SLAS506B – NOVEMBER 2006 – REVISED DECEMBER 2008

The TLV320DAC32 is a highly flexible, low power stereo audio DAC with extensive feature integration, intended

for application in smartphones, PDAs, and portable computing, communication, and entertainment applications.

Available in a 5x5mm 32-lead QFN, the product integrates a host of features to reduce cost, board space, and

power consumption in space-constrained, battery powered portable applications.

The TLV320DAC32 consists of the following blocks:

Stereo audio multi-bit delta-sigma DAC (8 kHz – 96 kHz)

Programmable digital audio effects processing (3-D, bass, treble, mid-range, EQ, de-emphasis)

Two analog audio input pins

Four high-power audio output drivers (headphone/speaker drive capability)

Fully programmable PLL

Programmable voltage level for microphone biasing

Headphone/headset jack detection with interrupt

Selectable internal LDO regulator for systems that only have +3.3V power available.

The I2C interface supports both standard and fast communication modes.

The TLV320DAC32 includes a LDO voltage regulator that can be used in systems where a 1.8V power supply is

not available. In systems where the LDO is used, 3.3V power is applied to the device, and the internal LDO

regulator generates the 1.8V needed to operate the internal digital core. The LDO functionality is controlled by

the state of the LDO_SELECT pin (pin 5 in QFN package). To enable the LDO function, apply IOVDD to the

LDO_SELECT pin. To disable the LDO function, connect the LDO_SELECT pin to ground. The correct operation

of the device requires that the LDO_SELECT pin must be connected to either IOVDD or ground. When the LDO

is bypassed, the DVDD pin must be connected to a 1.8V power supply.

A small value ceramic capacitor should be connected between the DVDD pin and digital ground, even when the

internal LDO is used. This capacitor provides power supply decoupling for either power supply condition. See

A.

See tables for voltage range of IOVDD

Figure 21. LDO Function Operating

Copyright 2006–2008, Texas Instruments Incorporated

19

Product Folder Link(s): TLV320DAC32

相關PDF資料 |

PDF描述 |

|---|---|

| TLV320DAC32IRHBRG4 | SERIAL INPUT LOADING, DAC WITH PROGRAMMABLE PLL, PQCC32 |

| TLV431AIDBV | 1-OUTPUT TWO TERM VOLTAGE REFERENCE, 1.24 V, PDSO5 |

| TLV431ALPRE | 1-OUTPUT TWO TERM VOLTAGE REFERENCE, PBCY3 |

| TLV431ALP | 1-OUTPUT TWO TERM VOLTAGE REFERENCE, PBCY3 |

| TLV431ALPRF | 1-OUTPUT TWO TERM VOLTAGE REFERENCE, PBCY3 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TLV320DAC32IRHBTG4 | 功能描述:音頻數/模轉換器 IC Low Power Stereo DAC RoHS:否 制造商:Texas Instruments 轉換器數量: 分辨率:16 bit 接口類型:I2S, UBS 轉換速率: 信噪比:98 dB 工作電源電壓:5 V DAC 輸出端數量:2 工作溫度范圍:- 25 C to + 85 C 電源電流:23 mA 安裝風格:SMD/SMT 封裝 / 箱體:TQFP-32 封裝:Reel |

| TLV320DAC33NIZQC | 制造商:Texas Instruments 功能描述: |

| TLV320DAC33NIZQCR | 制造商:Texas Instruments 功能描述: |

| TLV320VD30 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:VDSL CODEC |

| TLV320VD30PN | 制造商:Texas Instruments 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。