- 您現在的位置:買賣IC網 > PDF目錄98255 > TLV320DAC32IRHBT (TEXAS INSTRUMENTS INC) SERIAL INPUT LOADING, DAC WITH PROGRAMMABLE PLL, PQCC32 PDF資料下載

參數資料

| 型號: | TLV320DAC32IRHBT |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | DAC |

| 英文描述: | SERIAL INPUT LOADING, DAC WITH PROGRAMMABLE PLL, PQCC32 |

| 封裝: | 5 X 5 MM, GREEN, PLASTIC, QFN-32 |

| 文件頁數: | 20/69頁 |

| 文件大小: | 1242K |

| 代理商: | TLV320DAC32IRHBT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁

www.ti.com........................................................................................................................................ SLAS506B – NOVEMBER 2006 – REVISED DECEMBER 2008

J = 1, 2, 3, …, 63

D = 0000, 0001, 0002, 0003, …, 9998, 9999

PLLCLK_IN can be MCLK or BCLK, selected by Page 0, register 102, bits D5-D4

P, R, J, and D are register programmable. J is the integer portion of K (the numbers to the left of the decimal

point), while D is the fractional portion of K (the numbers to the right of the decimal point, assuming four digits of

precision).

Examples:

If K = 8.5, then J = 8, D = 5000

If K = 7.12, then J = 7, D = 1200

If K = 14.03, then J = 14, D = 0300

If K = 6.0004, then J = 6, D = 0004

When the PLL is enabled and D = 0000, the following conditions must be satisfied to meet specified

performance:

2 MHz

≤ ( PLLCLK_IN / P ) ≤ 20 MHz

80 MHz

≤ (PLLCLK _IN

K

R / P )

≤ 110 MHz

4

≤ J ≤ 55

When the PLL is enabled and D

≠0000, the following conditions must be satisfied to meet specified performance:

10 MHz

≤ PLLCLK _IN / P ≤ 20 MHz

80 MHz

≤ PLLCLK _IN

K

R / P

≤ 110 MHz

4

≤ J ≤ 11

R = 1

Example:

MCLK = 12 MHz and Fsref = 44.1 kHz

Select P = 1, R = 1, K = 7.5264, which results in J = 7, D = 5264

Example:

MCLK = 12 MHz and Fsref = 48.0 kHz

Select P = 1, R = 1, K = 8.192, which results in J = 8, D = 1920

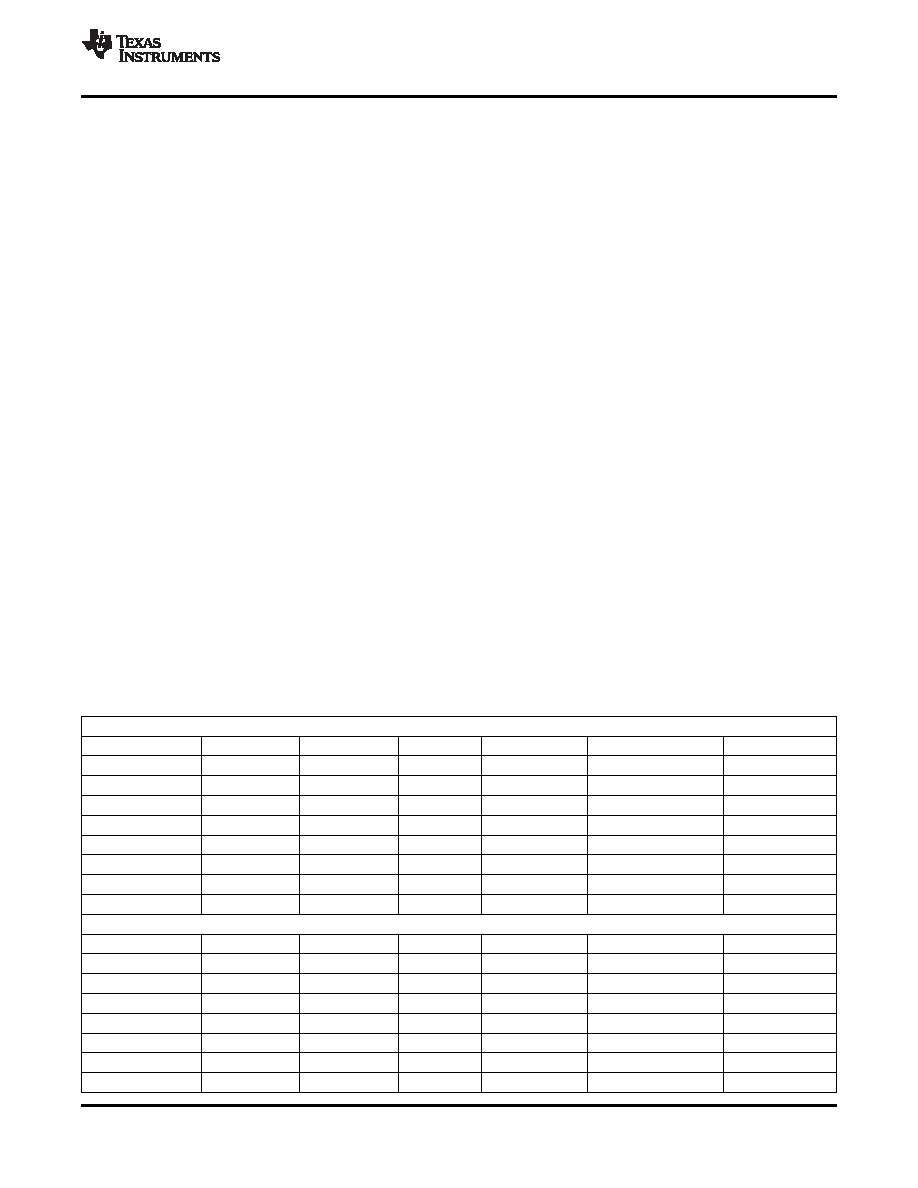

The table below lists several example cases of typical MCLK rates and how to program the PLL to achieve Fsref

= 44.1 kHz or 48 kHz.

Fsref = 44.1 kHz

MCLK (MHz)

P

R

J

D

ACHIEVED FSREF

% ERROR

2.8224

1

32

0

44100.00

0.0000

5.6448

1

16

0

44100.00

0.0000

12.0

1

7

5264

44100.00

0.0000

13.0

1

6

9474

44099.71

0.0007

16.0

1

5

6448

44100.00

0.0000

19.2

1

4

7040

44100.00

0.0000

19.68

1

4

5893

44100.30

–0.0007

48.0

4

1

7

5264

44100.00

0.0000

Fsref = 48 kHz

MCLK (MHz)

P

R

J

D

ACHIEVED FSREF

% ERROR

2.048

1

48

0

48000.00

0.0000

3.072

1

32

0

48000.00

0.0000

4.096

1

24

0

48000.00

0.0000

6.144

1

16

0

48000.00

0.0000

8.192

1

12

0

48000.00

0.0000

12.0

1

8

1920

48000.00

0.0000

13.0

1

7

5618

47999.71

0.0006

Copyright 2006–2008, Texas Instruments Incorporated

27

Product Folder Link(s): TLV320DAC32

相關PDF資料 |

PDF描述 |

|---|---|

| TLV320DAC32IRHBRG4 | SERIAL INPUT LOADING, DAC WITH PROGRAMMABLE PLL, PQCC32 |

| TLV431AIDBV | 1-OUTPUT TWO TERM VOLTAGE REFERENCE, 1.24 V, PDSO5 |

| TLV431ALPRE | 1-OUTPUT TWO TERM VOLTAGE REFERENCE, PBCY3 |

| TLV431ALP | 1-OUTPUT TWO TERM VOLTAGE REFERENCE, PBCY3 |

| TLV431ALPRF | 1-OUTPUT TWO TERM VOLTAGE REFERENCE, PBCY3 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TLV320DAC32IRHBTG4 | 功能描述:音頻數/模轉換器 IC Low Power Stereo DAC RoHS:否 制造商:Texas Instruments 轉換器數量: 分辨率:16 bit 接口類型:I2S, UBS 轉換速率: 信噪比:98 dB 工作電源電壓:5 V DAC 輸出端數量:2 工作溫度范圍:- 25 C to + 85 C 電源電流:23 mA 安裝風格:SMD/SMT 封裝 / 箱體:TQFP-32 封裝:Reel |

| TLV320DAC33NIZQC | 制造商:Texas Instruments 功能描述: |

| TLV320DAC33NIZQCR | 制造商:Texas Instruments 功能描述: |

| TLV320VD30 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:VDSL CODEC |

| TLV320VD30PN | 制造商:Texas Instruments 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。