- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365968 > TSB14AA1 FPGA (Field-Programmable Gate Array) PDF資料下載

參數(shù)資料

| 型號(hào): | TSB14AA1 |

| 英文描述: | FPGA (Field-Programmable Gate Array) |

| 中文描述: | 電機(jī)及電子學(xué)工程師聯(lián)合會(huì)1394-1995。 3.3。 1-port.50/100Mbps。底板PHY |

| 文件頁(yè)數(shù): | 23/35頁(yè) |

| 文件大小: | 224K |

| 代理商: | TSB14AA1 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)當(dāng)前第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)

6

–

3

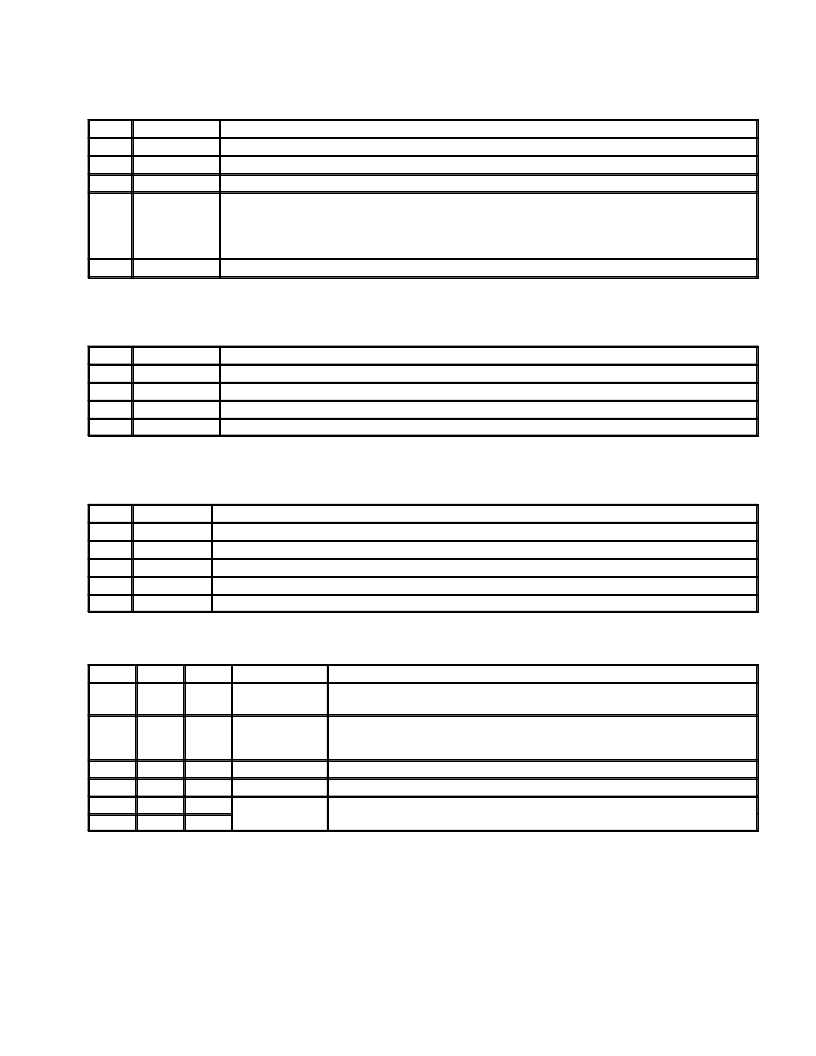

Table 6

–

5. Bus Request for Backplane Environment

BIT(s)

NAME

DESCRIPTION

0

Start bit

Indicates the beginning of the transfer (always 1)

1

–

3

Request type

Indicates the type of bus request (see Table 6

–

8 for the encoding of this field)

4

–

5

Request speed

Ignored (set to 00 for cable S100) for backplane environment

6

–

9

Request priority

Indicates the priority of urgent requests. It is only used with a FairReq request type. All zeros indicate a fair

request.

All ones are reserved (this priority is implied by a PriReq).

Other values are used to indicate the priority of an urgent request.

10

Stop bit

Indicates the end of the transfer (always 0)

For a Read Register Request the length of the LREQ data stream is 9 bits as shown in Table 6

–

6 (also see

Table 3

–

2 for the bit definitions).

Table 6

–

6. Read Request Format

BIT(s)

NAME

DESCRIPTION

0

Start bit

Indicates the beginning of the transfer (always 1).

1

–

3

Request type

Always a 100 indicating that this is a read register request.

4

–

7

Address

The address of the PHY register to be read.

8

Stop bit

Indicates the end of the transfer (always 0).

For a Write Register Request the length of the LREQ data stream is 17 bits as shown in Table 6

–

7 (see Table 3

–

1

for the bit field format).

Table 6

–

7. Write Request Format

BIT(s)

NAME

DESCRIPTION

0

Start bit

Indicates the beginning of the transfer (always 1)

1

–

3

Request type

Always 101b indicating that this is a write register request

4

–

7

Address

The address of the PHY register to be written to

8

–

15

Data

The data that is to be written to the specified register address

16

Stop bit

Indicates the end of the transfer (always 0)

The 3-bit request field is defined in Table 6

–

8.

Table 6

–

8. Request Field

LREQ1

LREQ2

LREQ3

NAME

DESCRIPTION

0

0

0

ImmReq

Immediate request. When an idle is detected, the PHY takes control of the bus immediately

(no arbitration).

0

1

1

Fair/Urgent Req

Fair or urgent request. The PHY arbitrates after a subaction gap using fair protocol.

Fair/Urgent Req is used for fair transfers with the request priority field differentiating fair and

urgent transfers for the backplane environment.

1

0

0

RdReq

Read register. Returns the specified register contents through a status transfer.

1

0

1

WrReq

Write register. Writes to the specified register.

1

1

0

Reserved

Reserved

1

1

1

LREQ Timing is shown in Figure 6

–

2. Each cell represents one clock sample time.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSB14AA1I | FPGA (Field-Programmable Gate Array) |

| TSB14AA1T | FPGA (Field-Programmable Gate Array) |

| TSB14C01MHV | IC APEX 20KE FPGA 160K 484-FBGA |

| TSB14C01HV | 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB21LV03MHV | IC APEX 20KE FPGA 200K 484-FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB14AA1A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:3.3 V IEEE 1394-1995 BACKPLANE PHY |

| TSB14AA1AI | 制造商:TI 制造商全稱:Texas Instruments 功能描述:3.3 V IEEE 1394-1995 BACKPLANE PHY |

| TSB14AA1AIPFB | 功能描述:1394 接口集成電路 IEEE139419953.3V1prt 50/100Mbps BkplnPHY RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB14AA1AIPFBG4 | 功能描述:1394 接口集成電路 3.3V 1-port 50/100 Mbps Backplane PHY RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB14AA1APFB | 功能描述:1394 接口集成電路 3.3V 1-port 50/100 Mbps Backplane PHY RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。