- 您現在的位置:買賣IC網 > PDF目錄373914 > AD7707 (Analog Devices, Inc.) ECONOLINE: REC2.2-S_DR/H1 - 2.2W DIP Package- 1kVDC Isolation- Regulated Output- UL94V-0 Package Material- Continuous Short Circiut Protection- Internal SMD design- 100% Burned In- Efficiency to 75% PDF資料下載

參數資料

| 型號: | AD7707 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | ECONOLINE: REC2.2-S_DR/H1 - 2.2W DIP Package- 1kVDC Isolation- Regulated Output- UL94V-0 Package Material- Continuous Short Circiut Protection- Internal SMD design- 100% Burned In- Efficiency to 75% |

| 中文描述: | 3 V / 5號第五,1毫瓦3 -10 V輸入范圍通道16位Σ-Δ模數轉換器 |

| 文件頁數: | 28/40頁 |

| 文件大小: | 316K |

| 代理商: | AD7707 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

REV. A

AD7707

–28–

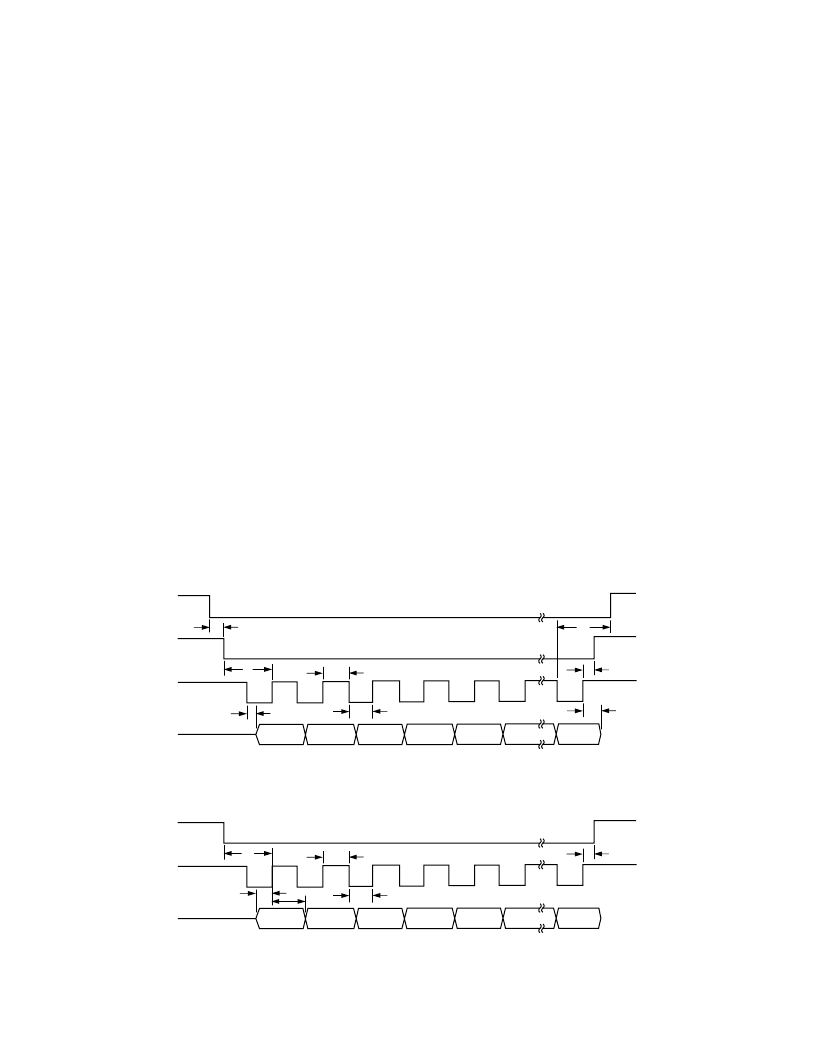

DRDY

CS

t

3

t

4

t

6

t

7

t

5

t

10

t

9

t

8

SCLK

DOUT

MSB

LSB

Figure 18. Read Cycle Timing Diagram

CS

t

11

t

14

t

15

t

12

t

16

SCLK

DIN

MSB

LSB

t

13

Figure 19. Write Cycle Timing Diagram

Figures 18 and 19 show timing diagrams for interfacing to the

AD7707 with

CS

used to decode the part. Figure 17 is for a

read operation from the AD7707’s output shift register while

Figure 18 shows a write operation to the input shift register. It is

possible to read the same data twice from the output register

even though the

DRDY

line returns high after the first read

operation. Care must be taken, however, to ensure that the read

operations have been completed before the next output update

is about to take place.

The AD7707 serial interface can operate in three-wire mode by

tying the

CS

input low. In this case, the SCLK, DIN and DOUT

lines are used to communicate with the AD7707 and the status

of

DRDY

can be obtained by interrogating the MSB of the

Communications Register. This scheme is suitable for interfac-

ing to microcontrollers. If

CS

is required as a decoding signal, it

can be generated from a port bit. For microcontroller interfaces,

it is recommended that the SCLK idles high between data

transfers.

The AD7707 can also be operated with

CS

used as a frame

synchronization signal. This scheme is suitable for DSP inter-

faces. In this case, the first bit (MSB) is effectively clocked out

by

CS

since

CS

would normally occur after the falling edge of

SCLK in DSPs. The SCLK can continue to run between data

transfers provided the timing numbers are obeyed.

The serial interface can be reset by exercising the

RESET

input

on the part. It can also be reset by writing a series of 1s on the

DIN input. If a Logic 1 is written to the AD7707 DIN line for

at least 32 serial clock cycles the serial interface is reset. This

ensures that in three-wire systems, if the interface gets lost either

via a software error or by some glitch in the system, it can be

reset back to a known state. This state returns the interface to

where the AD7707 is expecting a write operation to its Commu-

nications Register. This operation in itself does not reset the

contents of any registers but since the interface was lost, the

information written to any of the registers is unknown and it is

advisable to set up all registers again.

Some microprocessor or microcontroller serial interfaces have a

single serial data line. In this case, it is possible to connect the

AD7707’s DATA OUT and DATA IN lines together and con-

nect them to the single data line of the processor. A 10 k

pull-

up resistor should be used on this single data line. In this case, if

the interface gets lost, because the read and write operations

share the same line the procedure to reset it back to a known

state is somewhat different than previously described. It requires

a read operation of 24 serial clocks followed by a write operation

where a Logic 1 is written for at least 32 serial clock cycles to

ensure that the serial interface is back into a known state.

CONFIGURING THE AD7707

The AD7707 contains six on-chip registers that the user can

accesses via the serial interface. Communication with any of

these registers is initiated by writing to the Communications

Register first. Figure 20 outlines a flow diagram of the sequence

used to configure all registers after a power-up or reset on the

AD7707. The flowchart also shows two different read options—

the first where the

DRDY

pin is polled to determine when an

update of the data register has taken place, the second where the

DRDY

bit of the Communications Register is interrogated to

see if a data register update has taken place. Also included in the

flowing diagram is a series of words that should be written to the

registers for a particular set of operating conditions. These con-

ditions are gain of one, no filter sync, bipolar mode, buffer off,

clock of 4.9512MHz and an output rate of 50 Hz.

相關PDF資料 |

PDF描述 |

|---|---|

| AD7707EB | 3 V/5 V 610 V Input Range 1 mW 3-Channel 16-Bit Sigma-Delta ADC(316.51 k) |

| AD7708BR | Shaft; Style: 2 - light; Applicable Model: LE-P / LEL-W |

| AD7708BRU | 8-/10-Channel, Low Voltage, Low Power, ADCs |

| AD7708 | 8-/10-Channel, Low Voltage, Low Power, ADCs |

| AD7718 | 8-/10-Channel, Low Voltage, Low Power, ADCs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7707BR | 功能描述:IC ADC 16BIT 3CH 20-SOIC RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1,000 系列:- 位數:12 采樣率(每秒):300k 數據接口:并聯 轉換器數目:1 功率耗散(最大):75mW 電壓電源:單電源 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:24-SOIC(0.295",7.50mm 寬) 供應商設備封裝:24-SOIC 包裝:帶卷 (TR) 輸入數目和類型:1 個單端,單極;1 個單端,雙極 |

| AD7707BR-REEL | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 500sps 16-bit Serial 20-Pin SOIC W T/R 制造商:Analog Devices 功能描述:ADC SGL DELTA-SIGMA 0.5KSPS 16BIT SERL 20SOIC W - Tape and Reel |

| AD7707BR-REEL7 | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 500sps 16-bit Serial 20-Pin SOIC W T/R 制造商:Analog Devices 功能描述:ADC SGL DELTA-SIGMA 0.5KSPS 16BIT SERL 20SOIC W - Tape and Reel |

| AD7707BRU | 功能描述:IC ADC 16BIT 3CH 20-TSSOP RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1,000 系列:- 位數:12 采樣率(每秒):300k 數據接口:并聯 轉換器數目:1 功率耗散(最大):75mW 電壓電源:單電源 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:24-SOIC(0.295",7.50mm 寬) 供應商設備封裝:24-SOIC 包裝:帶卷 (TR) 輸入數目和類型:1 個單端,單極;1 個單端,雙極 |

| AD7707BRU-REEL | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 500sps 16-bit Serial 20-Pin TSSOP T/R 制造商:Analog Devices 功能描述:ADC SGL DELTA-SIGMA 0.5KSPS 16BIT SERL 20TSSOP - Tape and Reel |

發布緊急采購,3分鐘左右您將得到回復。