- 您現在的位置:買賣IC網 > PDF目錄373915 > AD7722AS (ANALOG DEVICES INC) 16-Bit, 195 kSPS CMOS, Sigma-Delta ADC PDF資料下載

參數資料

| 型號: | AD7722AS |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 16-Bit, 195 kSPS CMOS, Sigma-Delta ADC |

| 中文描述: | 1-CH 16-BIT DELTA-SIGMA ADC, SERIAL/PARALLEL ACCESS, PQFP44 |

| 封裝: | MS-022AA, MQFP-44 |

| 文件頁數: | 7/24頁 |

| 文件大小: | 526K |

| 代理商: | AD7722AS |

AD7722

–7–

REV. 0

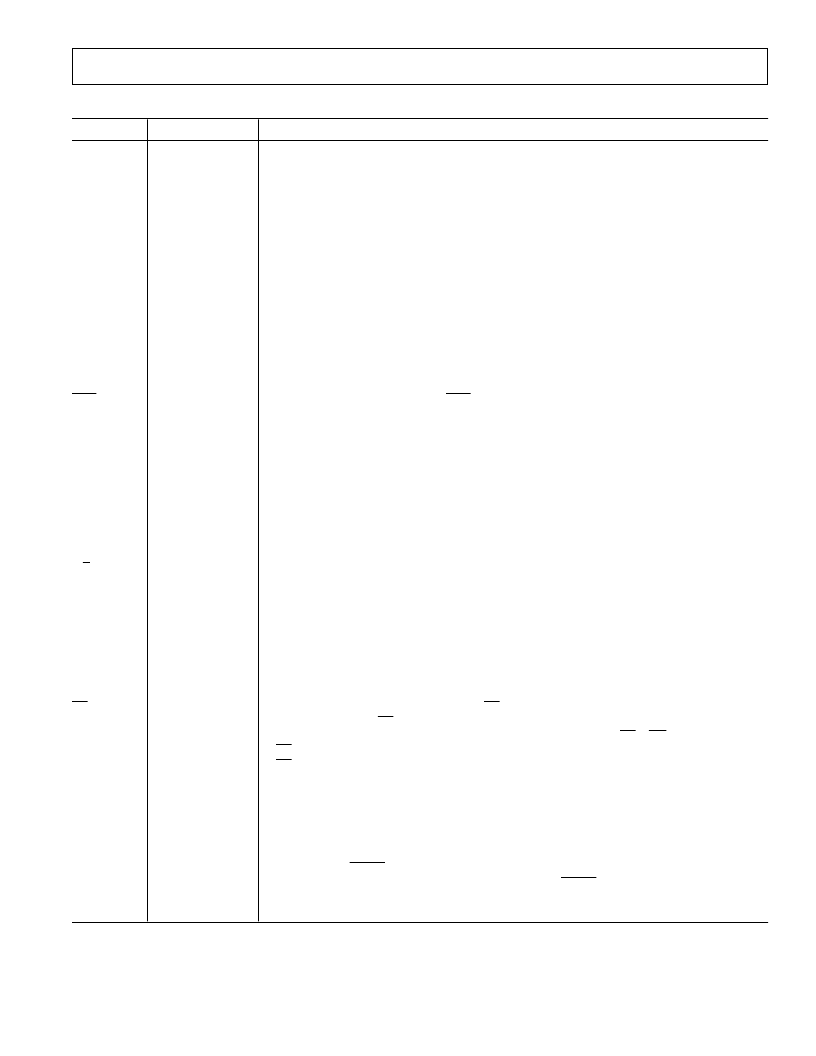

PIN FUNCTION DESCRIPTION

Mnemonic

Pin No.

Description

AV

DD1

AGND1

AV

DD

AGND

14

10

20, 23

9, 13, 15,

19, 21, 25, 26

39

6, 28

22

Clock logic power supply voltage for the analog modulator, +5 V

±

5%.

Clock logic ground reference for the analog modulator.

Analog Power Supply Voltage, +5 V

±

5%.

Ground reference for analog circuitry.

DV

DD

DGND

REF1

Digital Power Supply Voltage, +5 V

±

5%.

Ground reference for digital circuitry.

Reference Input/Output. REF1 connects through 3 k

to the output of the internal 2.5 V

reference and to the input of a buffer amplifier that drives the

Σ

modulator. This pin can

also be overdriven with an external reference 2.5 V.

Reference Input/Output. REF2 connects to the output of an internal buffer amplifier used to

to drive the

Σ

modulator. When REF2 is used as an input, REF1 must be connected

to AGND.

Positive terminal of the differential analog input.

Negative terminal of the differential analog input.

Analog input range select input.

UNI

selects the analog input range for either bipolar

or unipolar operation. A logic low input selects unipolar operation. A logic high input

selects bipolar operation.

Clock Input. Master clock signal for the device. The CLKIN pin interfaces the AD7722

internal oscillator circuit to an external crystal or to an external clock. A parallel resonant,

fundamental-frequency, microprocessor-grade crystal and a 1 M

resistor should be

connected between the CLKIN and XTAL pin with two capacitors connected from each

pin to ground. Alternatively, the CLKIN pin can be driven with an external CMOS-

compatible clock. The AD7722 is specified with a clock input frequency of 12.5 MHz.

Oscillator Output. The XTAL pin connects the internal oscillator output to an external

crystal. If an external clock is used, XTAL should be left unconnected.

Parallel/Serial interface select input. A logic high configures output data interface for parallel

mode operation. Serial mode operation is selected with the P/S set to a logic low.

Calibration Logic Input. A logic high input for a duration of one CLKIN cycle initiates a

calibration sequence for the device Gain and Offset Error.

Reset Logic Input. RESET is used to clear the offset and gain calibration registers. RESET is an

asynchronous input. RESET allows the user to set AD7722 to an uncalibrated state if the device

had been previously calibrated. A rising edge also resets the AD7722

Σ

modulator by shorting

the integrator capacitors in the modulator. In addition RESET functions identically to the

SYNC pin described below.

Chip select is a level sensitive logic input.

CS

enables the output data register for parallel mode

read operation. The

CS

logic level is sensed on the rising edge of CLKIN. The output data bus

is enabled when the rising edge of CLKIN senses a logic low level on

CS

if

RD

is also low. When

CS

is sensed high, the output data bits DB15–DB0 will be high impedance. In serial mode tie

CS

to a logic low.

Synchronization Logic Input. SYNC is an asynchronous input. When using more than one

AD7722 operated from a common master clock, SYNC allows each ADC’s

Σ

modulator

to simultaneously sample its analog input and update its output data register. A rising edge resets

the AD7722 digital filter sequencer counter to zero. After a SYNC, conversion data is not valid

until after the digital filter settles (reference Figure 7). DVAL goes low in the serial mode. When

the rising edge of CLKIN senses a logic low on SYNC (or RESET) the reset state is released; in

parallel mode,

DRDY

goes high. After the reset state is released, DVAL returns high after

8192 CLKIN cycles (128

×

64/f

CLKIN

); in parallel mode,

DRDY

returns low after one additional

convolution cycle of the digital filter (64 CLKIN periods), when valid data is ready to be read

from the output data register.

REF2

24

V

IN

(+)

V

IN

(–)

UNI

18

16

7

CLKIN

11

XTAL

12

P/

S

8

CAL

27

RESET

17

CS

29

SYNC

30

相關PDF資料 |

PDF描述 |

|---|---|

| AD7723 | 16-Bit, 1.2 MSPS CMOS, Sigma-Delta ADC |

| AD7723BS | 16-Bit, 1.2 MSPS CMOS, Sigma-Delta ADC |

| AD7724AST | Dual CMOS Modulators |

| AD7724 | Dual CMOS Modulators |

| AD7725 | 16-Bit 900 kSPS ADC with a Programmable Postprocessor |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7722AS-ES | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD7722ASZ | 功能描述:IC ADC 16BIT 195KSPS 44-MQFP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD7722CSZ | 制造商:Analog Devices 功能描述: |

| AD7723 | 制造商:AD 制造商全稱:Analog Devices 功能描述:16-Bit, 1.2 MSPS CMOS, Sigma-Delta ADC |

| AD7723BS | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 19.2Msps 16-bit Parallel/Serial 44-Pin MQFP 制造商:Analog Devices 功能描述:Analog-Digital Converter IC Number of Bi |

發布緊急采購,3分鐘左右您將得到回復。