- 您現在的位置:買賣IC網 > PDF目錄373920 > AD7854L (Analog Devices, Inc.) 12-Bit Sampling ADC(單電源,200kSPS 12位采樣A/D轉換器) PDF資料下載

參數資料

| 型號: | AD7854L |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 12-Bit Sampling ADC(單電源,200kSPS 12位采樣A/D轉換器) |

| 中文描述: | 12位采樣ADC(單電源,速度高達200ksps的12位采樣的A / D轉換器) |

| 文件頁數: | 4/28頁 |

| 文件大小: | 268K |

| 代理商: | AD7854L |

第1頁第2頁第3頁當前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

AD7854/AD7854L

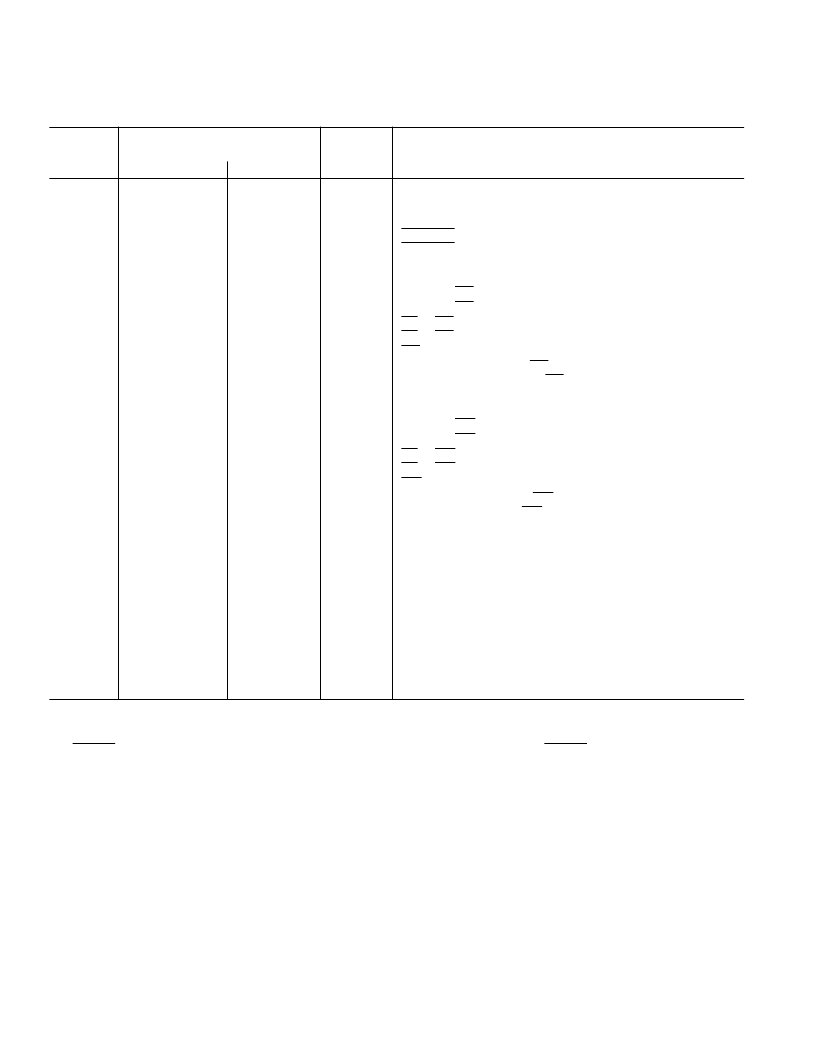

TIMNGSPECIFICATIONS

1

(AV

DD

= DV

DD

= +3.0 V to +5.5 V; f

CLKIN

= 4 MHz for AD7854 and 1.8 MHz for AD7854L;

T

A

= T

MN

to T

MAX

, unless otherwse noted)

–4–

REV. 0

Limit at T

MIN

, T

MAX

(A, B, S Versions)

Parameter

5 V

3 V

Units

Description

f

CLK IN2

500

4

1.8

100

50

4.5

10

15

5

0

0

55

50

5

40

60

0

5

0

0

55

10

5

1/2 t

CLK IN

50

50

40

40

2.5 t

CLK IN

31.25

500

4

1.8

100

90

4.5

10

15

5

0

0

70

50

5

40

70

0

5

0

0

70

10

5

1/2 t

CLK IN

70

70

60

60

2.5 t

CLK IN

31.25

kHz min

MHz max

MHz max

ns min

ns max

μ

s max

μ

s max

ns min

ns min

ns min

ns min

ns min

ns max

ns min

ns max

ns min

ns min

ns max

ns min

ns max

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns max

ms typ

Master Clock Frequency

L Version

CONVST

Pulse Width

CONVST

to BUSY

↑

Propagation Delay

Conversion T ime = 18 t

CLK IN

L Version 1.8 MHz CLK IN. Conversion T ime = 18 t

CLK IN

HBEN to RD

Setup T ime

HBEN to RD

Hold T ime

CS

to

RD

to Setup T ime

CS

to

RD

Hold T ime

RD

Pulse Width

Data Access T ime After

RD

Bus Relinquish T ime After

RD

t

13

t

2

t

CONVERT

t

3

t

4

t

5

t

6

t

7

t

84

t

95

t

10

t

11

t

12

t

13

t

14

t

15

t

16

t

17

t

184

t

19

t

20

t

21

t

22

t

23

t

CAL6

Minimum T ime Between Reads

HBEN to

WR

Setup T ime

HBEN to

WR

Hold T ime

CS

to

WR

Setup T ime

CS

to

WR

Hold T ime

WR

Pulse Width

Data

Setup

Time Before WR

Data Hold Time

After

WR

New Data Valid Before Falling Edge of BUSY

HBEN High Pulse Duration

HBEN Low Pulse Duration

Propagation Delay from HBEN Rising Edge to Data Valid

Propagation Delay from HBEN Falling Edge to Data Valid

CS

↑

to BUSY

↑

in Calibration Sequence

Full Self-Calibration T ime, Master Clock Dependent (125013

t

CLK IN

)

Internal DAC Plus System Full-Scale Cal T ime, Master Clock

Dependent (111124 t

CLK IN

)

System Offset Calibration T ime, Master Clock Dependent

(13889 t

CLK IN

)

t

CAL16

27.78

27.78

ms typ

t

CAL26

3.47

3.47

ms typ

NOT ES

1

Sample tested at +25

°

C to ensure compliance. All input signals are specified with tr = tf = 5 ns (10% to 90% of V

DD

) and timed from a voltage level of 1.6 V.

2

Mark/Space ratio for the master clock input is 40/60 to 60/40.

3

T he

CONVST

pulse width here only applies for normal operation. When the part is in power-down mode, a different

CONVST

pulse width applies (see Power-

Down section).

4

Measured with the load circuit of Figure 1 and defined as the time required for the output to cross 0.8 V or 2.4 V.

5

t

is derived form the measured time taken by the data outputs to change 0.5 V when loaded with the circuit of Figure 1. T he measured number is then extrapolated

back to remove the effects of charging or discharging the 50 pF capacitor. T his means that the time, t

9

, quoted in the timing characteristics is the true bus relinquish

time of the part and is independent of the bus loading.

6

T he typical time specified for the calibration times is for a master clock of 4 MHz. For the L version the calibration times will be longer than those quoted here due to

the 1.8 MHz master clock.

Specifications subject to change without notice.

相關PDF資料 |

PDF描述 |

|---|---|

| AD7854 | 12-Bit Sampling ADC(單電源,200kSPS 12位采樣A/D轉換器) |

| AD7858LARS | 3 V to 5 V Single Supply, 200 kSPS 8-Channel, 12-Bit Sampling ADC |

| AD7858BN | 3 V to 5 V Single Supply, 200 kSPS 8-Channel, 12-Bit Sampling ADC |

| AD7858BR | 3 V to 5 V Single Supply, 200 kSPS 8-Channel, 12-Bit Sampling ADC |

| AD7858AN | 3 V to 5 V Single Supply, 200 kSPS 8-Channel, 12-Bit Sampling ADC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7854LAQ | 制造商:Rochester Electronics LLC 功能描述:12 BIT SINGLE CHANNEL PARALLEL ADC I.C. - Bulk |

| AD7854LAR | 制造商:Analog Devices 功能描述:ADC Single SAR 100ksps 12-bit Parallel 28-Pin SOIC W 制造商:Rochester Electronics LLC 功能描述:12-BIT SINGLE CHANNEL PARALLEL ADC I.C. - Bulk |

| AD7854LAR-REEL | 制造商:Analog Devices 功能描述:ADC Single SAR 100ksps 12-bit Parallel 28-Pin SOIC W T/R 制造商:Analog Devices 功能描述:ADC SGL SAR 100KSPS 12-BIT PARALLEL 28SOIC W - Tape and Reel |

| AD7854LARS | 功能描述:IC ADC 12BIT PARALLEL LP 28-SSOP RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:2,500 系列:- 位數:12 采樣率(每秒):3M 數據接口:- 轉換器數目:- 功率耗散(最大):- 電壓電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 供應商設備封裝:SOT-23-6 包裝:帶卷 (TR) 輸入數目和類型:- |

發布緊急采購,3分鐘左右您將得到回復。