- 您現在的位置:買賣IC網 > PDF目錄373969 > AD9858BSV (ANALOG DEVICES INC) 1 GSPS Direct Digital Synthesizer PDF資料下載

參數資料

| 型號: | AD9858BSV |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數字信號處理外設 |

| 英文描述: | 1 GSPS Direct Digital Synthesizer |

| 中文描述: | DSP-NUM CONTROLLED OSCILLATOR, PQFP100 |

| 封裝: | PLASTIC, MS-026AED-HD, TQFP-100 |

| 文件頁數: | 23/32頁 |

| 文件大小: | 1412K |

| 代理商: | AD9858BSV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

AD9858

Serial Programming Mode

In serial programming mode, the I/O port uses a chip select pin

(CS), a serial clock pin (SCLK), an I/O reset pin (IORESET),

and either 1 or 2 serial data pins (SDIO and/or SDO). The

number of serial data pins used depends on the configuration

of the I/O port; i.e., whether it has been configured for 2-wire or

3-wire serial operation as defined by the control function

register. In 2-wire mode, the SDIO pin operates as a

bidirectional serial data pin. In 3-wire mode, the SDIO pin

operates only as a serial data input pin, and the SDO pin acts as

the serial output. The maximum rate of SCLK is 10 MHz;

however, during read operation, the 10 MHz rate is not

guaranteed.

Rev. A | Page 23 of 32

The serial port is an SPI compatible serial interface and its

operation is virtually identical to that of the AD9852/AD9854.

Serial port communication occurs in two phases. Phase 1 is an

instruction cycle consisting of an 8-bit word. The MSB of the

instruction byte flags the ensuing operation as a read or write

operation. The 6 LSBs define the serial address of the target

register as defined in the register map. The instruction byte

format is given in Table 5.

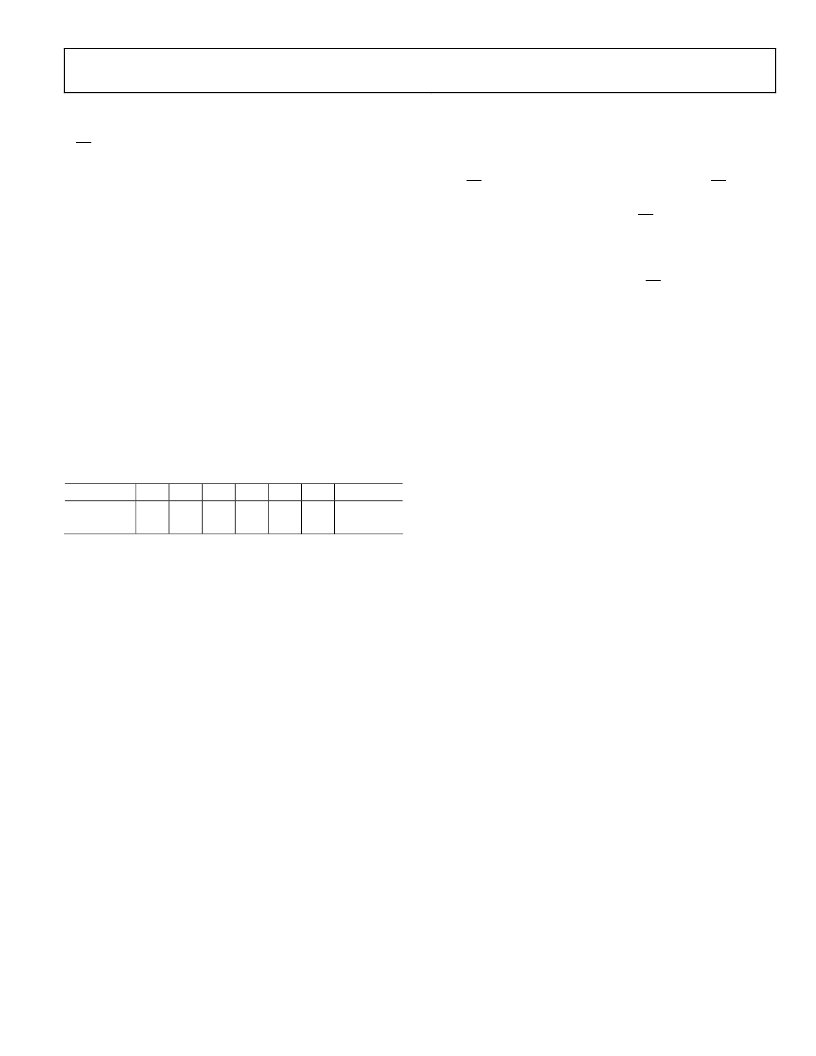

Table 5.

D7 (MSB)

D6

D5

D4

1: Read

0: Write

D3

A3

D2

A2

D1

A1

DO (LSB)

A0

X

A5

A4

Phase 2 of a serial port communication contains the data to be

routed to/from the addressed register. The number of bytes

transferred during Phase 2 depends on the length of the target

register. Serial operation requires that

all

bits associated with a

serial register address be transferred.

Both phases of a serial port communication require the serial

data clock (SCLK) to be operating. When writing to the device,

serial bits are transferred on the rising edge of SCLK. When

reading from the device, serial output bits are transferred on the

falling edge of SCLK. The bit order for both phases of a serial

port communication is selectable via the control function

register.

The CS pin serves as a chip select control line. When CS is at a

Logic 1 state, the SDO and SDIO pins are disabled (forced into a

high impedance state). Only when the CS pin is at a Logic 0

state are the SDO and SDIO pins active. This allows multiple

devices to exist on a single serial bus. If multiple devices are

connected to the same serial bus, then communication with a

single device is accomplished by setting CS to a Logic 0 state on

the target device, but to a Logic 1 state on all other devices. In

this way, serial communication occurs only between the

controller and the target device.

In the case where I/O synchronization is lost between the

AD9858 and the external controller, the IORESET pin provides

a means to re-establish synchronization without initializing the

entire device. Asserting the active high IORESET pin resets the

serial port state machine. This terminates the current I/O

operation and puts the device into a state in which the next

eight SCLK pulses are expected to be the instruction byte of the

next I/O transfer. Note that any information previously written

to the memory registers during the last valid communication

cycle prior to loss of synchronization remains intact.

Register Map

The registers are listed in Table 6. The serial address and parallel

address numbers associated with each of the registers are shown

in hexadecimal format. Angle brackets <> are used to reference

specific bits or ranges of bits. For example, <3> designates Bit 3,

while <7:3> designates the range of bits from 7 down to 3,

inclusive.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9858PCB | 1 GSPS Direct Digital Synthesizer |

| AD9858 | 1 GSPS Direct Digital Synthesizer |

| AD9858FDPCB | 1 GSPS Direct Digital Synthesizer |

| AD9859 | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9859YSV | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9858BSVZ | 功能描述:IC DDS DAC 10BIT 1GSPS 100-TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 直接數字合成 (DDS) 系列:- 產品變化通告:Product Discontinuance 27/Oct/2011 標準包裝:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 調節字寬(位):32 b 電源電壓:2.97 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:帶卷 (TR) |

| AD9858FDPCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Direct Digital Synthesizer |

| AD9858PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Direct Digital Synthesizer |

| AD9858TLPCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Direct Digital Synthesizer |

| AD9858XSV | 制造商:Analog Devices 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。