- 您現在的位置:買賣IC網 > PDF目錄373971 > AD9927BBCZRL (ANALOG DEVICES INC) 14-Bit CCD Signal Processor with V-Driver and Precision TimingTM Generator PDF資料下載

參數資料

| 型號: | AD9927BBCZRL |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費家電 |

| 英文描述: | 14-Bit CCD Signal Processor with V-Driver and Precision TimingTM Generator |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, BGA128 |

| 封裝: | 9 X 9 MM, LEAD FREE, MO-225, CSP_BGA-128 |

| 文件頁數: | 16/100頁 |

| 文件大小: | 784K |

| 代理商: | AD9927BBCZRL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁

AD9927

HIGH SPEED

PRECISION TIMING

CORE

The AD9927 generates high speed timing signals using the

flexible

Precision Timing

core. This core is the foundation for

generating the timing used for both the CCD and the AFE; it

includes the reset gate RG, horizontal drivers H1 to H8, HL,

and SHP/SHD sample clocks. A unique architecture makes it

routine for the system designer to optimize image quality by

providing precise control over the horizontal CCD readout

and the AFE correlated double sampling.

Rev. 0 | Page 16 of 100

The high speed timing of the AD9927 operates the same

way in either master or slave mode configuration. For more

information on synchronization and pipeline delays, see

the Power-Up Sequence for Master Mode section.

Timing Resolution

The

Precision Timing

core uses a 1× master clock input as a

reference (CLI). This clock should be the same as the CCD pixel

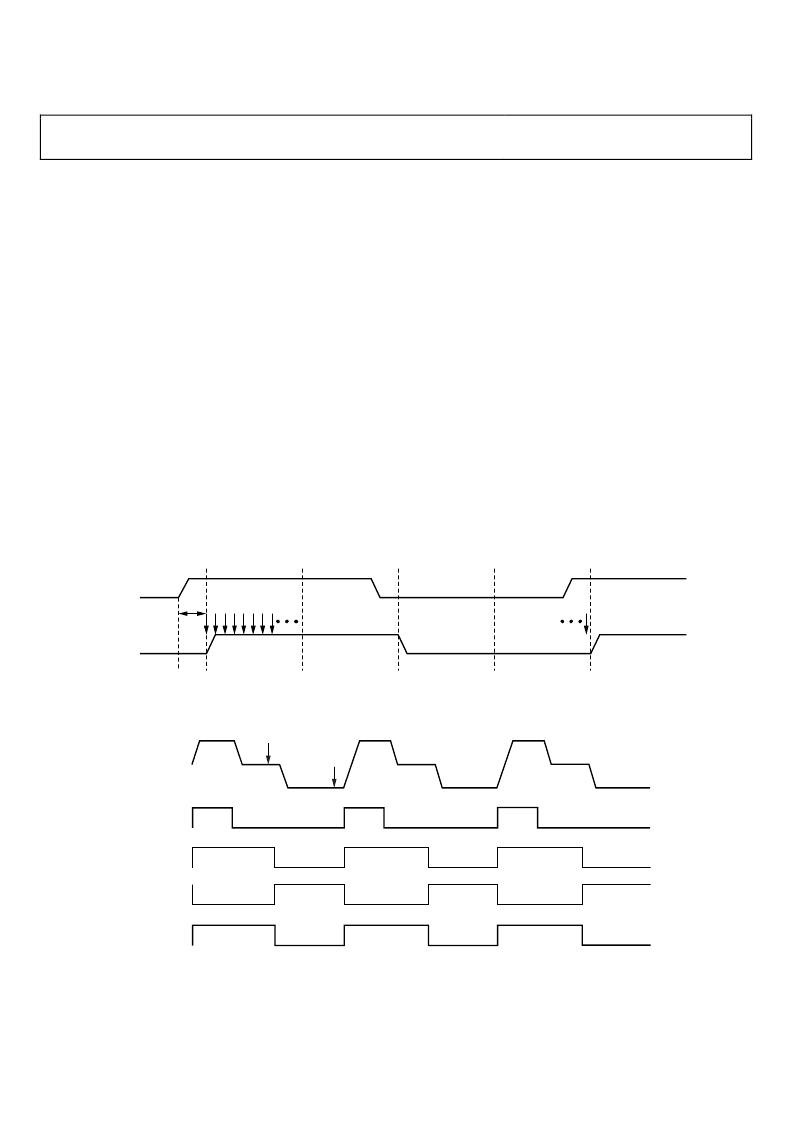

clock frequency. Figure 16 illustrates how the internal timing

core divides the master clock period into 64 steps or edge

positions. Using a 40 MHz CLI frequency, the edge resolution

of the

Precision Timing

core is approximately 0.4 ns. If a 1×

system clock is not available, it is possible to use a 2× reference

clock by programming the CLIDIVIDE register (AFE Register

Address 0x0D). The AD9927 then internally divides the CLI

frequency by 2.

The AD9927 includes a master clock output, CLO, which

is the inverse of CLI. This output should be used as a crystal

driver. A crystal can be placed between the CLI and CLO pins

to generate the master clock for the AD9927.

High Speed Clock Programmability

Figure 17 shows when the high speed clocks RG, H1 to H8,

SHP, and SHD are generated. The RG pulse has programmable

rising and falling edges and can be inverted using the polarity

control. Horizontal Clock H1 has programmable rising and

falling edges and polarity control. In HCLK Mode 1, H3, H5,

and H7 are equal to H1 and H2, H4, H6, and H8 are always

inverses of H1.

The edge location registers are each six bits wide, allowing the

selection of all 64 edge locations. Figure 20 shows the default

timing locations for all of the high speed clock signals.

P[0]

P[64] = P[0]

P[16]

P[32]

P[48]

ONE PIXEL

PERIOD

CLI

t

CLIDLY

POSITION

NOTES

1. THE PIXEL CLOCK PERIOD IS DIVIDED INTO 64 POSITIONS, PROVIDING FINE EDGE RESOLUTION FOR HIGH SPEED CLOCKS.

2. THERE IS A FIXED DELAY FROM THE CLI INPUT TO THE INTERNAL PIXEL PERIOD POSITION (t

CLIDLY

).

0

Figure 16. High Speed Clock Resolution from CLI, Master Clock Input

HL

CCD

SIGNAL

RG

PROGRAMMABLE CLOCK POSITIONS:

SHP SAMPLE LOCATION.

2

SHD SAMPLE LOCATION.

3

RG RISING EDGE.

4

RG FALLING EDGE.

5

H1 RISING EDGE.

6

H1 FALLING EDGE.

7

HL RISING EDGE.

8

HL FALLING EDGE.

1

2

3

4

7

8

H2, H4, H6, H8

H1, H3, H5, H7

5

6

0

Figure 17. High Speed Clock Programmable Locations (HCLKMODE = 001)

相關PDF資料 |

PDF描述 |

|---|---|

| AD9929BBCZ | CCD Signal Processor with Precision Timing Generator |

| AD9929 | CCD Signal Processor with Precision Timing Generator |

| AD9937 | CCD Signal Processor with Precision Timing⑩ Generator |

| AD9937KCP | CCD Signal Processor with Precision Timing⑩ Generator |

| AD9937KCPRL | TVPS00RF-25-35PB W/ PC CONTACT |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9928 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Dual Channel 14-Bit CCD Signal Processor with V-Driver and Precision Timing Generator |

| AD9928BBCZ | 功能描述:IC CCD SIGNAL PROCESSR 128CSPBGA RoHS:是 類別:集成電路 (IC) >> 線性 - 視頻處理 系列:- 產品變化通告:Product Discontinuation 07/Mar/2011 標準包裝:3,000 系列:OMNITUNE™ 類型:調諧器 應用:移動電話,手機,視頻顯示器 安裝類型:表面貼裝 封裝/外殼:65-WFBGA 供應商設備封裝:PG-WFSGA-65 包裝:帶卷 (TR) 其它名稱:SP000365064 |

| AD9928BBCZ-60 | 制造商:Analog Devices 功能描述:- Trays |

| AD9928BBCZRL | 功能描述:IC CCD SIGNAL PROCESSR 128CSPBGA RoHS:否 類別:集成電路 (IC) >> 線性 - 視頻處理 系列:- 產品變化通告:Product Discontinuation 07/Mar/2011 標準包裝:3,000 系列:OMNITUNE™ 類型:調諧器 應用:移動電話,手機,視頻顯示器 安裝類型:表面貼裝 封裝/外殼:65-WFBGA 供應商設備封裝:PG-WFSGA-65 包裝:帶卷 (TR) 其它名稱:SP000365064 |

| AD9928XBCZ-60 | 功能描述:IC CCD SIGNAL PROCESSOR 制造商:analog devices inc. 系列:- 包裝:托盤 零件狀態:上次購買時間 類型:CCD 信號處理器,14 位 應用:照相機 安裝類型:表面貼裝 封裝/外殼:128-LFBGA,CSPBGA 供應商器件封裝:128-CSPBGA(9x9) 標準包裝:1 |

發布緊急采購,3分鐘左右您將得到回復。