- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373971 > AD9927BBCZRL (ANALOG DEVICES INC) 14-Bit CCD Signal Processor with V-Driver and Precision TimingTM Generator PDF資料下載

參數(shù)資料

| 型號(hào): | AD9927BBCZRL |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | 14-Bit CCD Signal Processor with V-Driver and Precision TimingTM Generator |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, BGA128 |

| 封裝: | 9 X 9 MM, LEAD FREE, MO-225, CSP_BGA-128 |

| 文件頁數(shù): | 6/100頁 |

| 文件大小: | 784K |

| 代理商: | AD9927BBCZRL |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁

AD9927

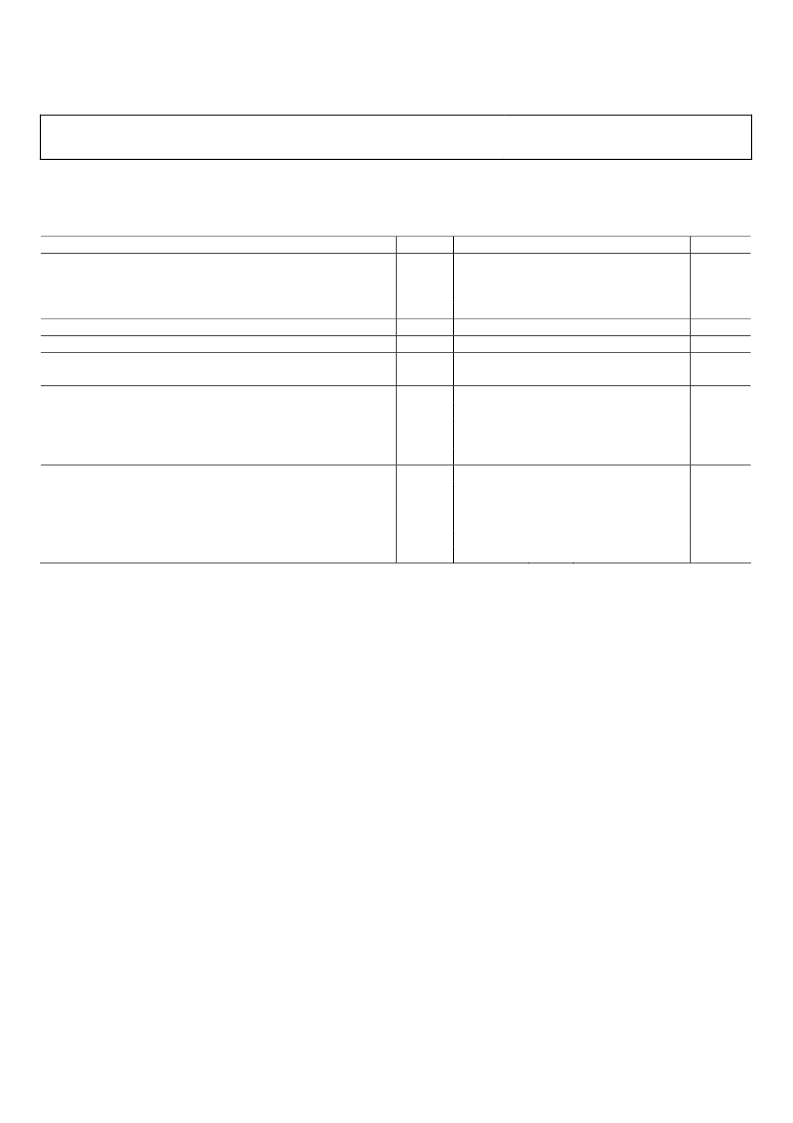

TIMING SPECIFICATIONS

C

L

= 20 pF, AVDD = DVDD = TCVDD = 1.8 V, DRVDD = 3.0 V, f

CLI

= 40 MHz, unless otherwise noted.

Table 4.

Parameter

MASTER CLOCK (See Figure 16)

CLI Clock Period

CLI High/Low Pulse Width

Delay from CLI Rising Edge to Internal Pixel Position 0

VD FALLING EDGE TO HD FALLING EDGE IN SLAVE MODE (See Figure 89)

AFE CLPOB PULSE WIDTH (See Figure 23 and Figure 33)

1, 2

AFE SAMPLE LOCATION (See Figure 17 and Figure 20)

1

SHP Sample Edge to SHD Sample Edge

DATA OUTPUTS (See Figure 21 and Figure 22)

Output Delay from DCLK Rising Edge

Inhibited Area for DOUTPHASE Edge Location

Rev. 0 | Page 6 of 100

Symbol

t

CONV

t

CLIDLY

t

VDHD

t

S1

t

OD

t

DOUTINH

Min

25

10

0

2

11

SHDLOC + 1

Typ

12.5

6

20

12.5

1

Max

15

VD period 5 × t

CONV

SHDLOC + 15

Unit

ns

ns

ns

ns

Pixels

ns

ns

Edge

location

Cycles

MHz

ns

ns

ns

ns

Pipeline Delay from SHP/SHD Sampling to DOUT

SERIAL INTERFACE (See Figure 97)

Maximum SCK Frequency (Must Not Exceed CLI Frequency)

SL to SCK Setup Time

SCK to SL Hold Time

SDATA Valid to SCK Rising Edge Setup

SCK Falling Edge to SDATA Valid Hold

1

Parameter is programmable.

2

Minimum CLPOB pulse width is for functional operation only. Wider typical pulses are recommended to achieve good clamp performance.

f

SCLK

t

LS

t

LH

t

DS

t

DH

40

10

10

10

10

16

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9929BBCZ | CCD Signal Processor with Precision Timing Generator |

| AD9929 | CCD Signal Processor with Precision Timing Generator |

| AD9937 | CCD Signal Processor with Precision Timing⑩ Generator |

| AD9937KCP | CCD Signal Processor with Precision Timing⑩ Generator |

| AD9937KCPRL | TVPS00RF-25-35PB W/ PC CONTACT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9928 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Dual Channel 14-Bit CCD Signal Processor with V-Driver and Precision Timing Generator |

| AD9928BBCZ | 功能描述:IC CCD SIGNAL PROCESSR 128CSPBGA RoHS:是 類別:集成電路 (IC) >> 線性 - 視頻處理 系列:- 產(chǎn)品變化通告:Product Discontinuation 07/Mar/2011 標(biāo)準(zhǔn)包裝:3,000 系列:OMNITUNE™ 類型:調(diào)諧器 應(yīng)用:移動(dòng)電話,手機(jī),視頻顯示器 安裝類型:表面貼裝 封裝/外殼:65-WFBGA 供應(yīng)商設(shè)備封裝:PG-WFSGA-65 包裝:帶卷 (TR) 其它名稱:SP000365064 |

| AD9928BBCZ-60 | 制造商:Analog Devices 功能描述:- Trays |

| AD9928BBCZRL | 功能描述:IC CCD SIGNAL PROCESSR 128CSPBGA RoHS:否 類別:集成電路 (IC) >> 線性 - 視頻處理 系列:- 產(chǎn)品變化通告:Product Discontinuation 07/Mar/2011 標(biāo)準(zhǔn)包裝:3,000 系列:OMNITUNE™ 類型:調(diào)諧器 應(yīng)用:移動(dòng)電話,手機(jī),視頻顯示器 安裝類型:表面貼裝 封裝/外殼:65-WFBGA 供應(yīng)商設(shè)備封裝:PG-WFSGA-65 包裝:帶卷 (TR) 其它名稱:SP000365064 |

| AD9928XBCZ-60 | 功能描述:IC CCD SIGNAL PROCESSOR 制造商:analog devices inc. 系列:- 包裝:托盤 零件狀態(tài):上次購買時(shí)間 類型:CCD 信號(hào)處理器,14 位 應(yīng)用:照相機(jī) 安裝類型:表面貼裝 封裝/外殼:128-LFBGA,CSPBGA 供應(yīng)商器件封裝:128-CSPBGA(9x9) 標(biāo)準(zhǔn)包裝:1 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。