- 您現在的位置:買賣IC網 > PDF目錄373975 > ADATE207BBP (ANALOG DEVICES INC) Quad Pin Timing Formatter PDF資料下載

參數資料

| 型號: | ADATE207BBP |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費家電 |

| 英文描述: | Quad Pin Timing Formatter |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PBGA256 |

| 封裝: | MO-192-BAL-2, LBGA-256 |

| 文件頁數: | 16/36頁 |

| 文件大小: | 374K |

| 代理商: | ADATE207BBP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

ADATE207

After the power and MCLK inputs are stable, the device must be

reset using the hard reset and error reset bits. The soft reset can

be used to initialize registers at any time and does not reset the

PLL or FIFOs.

Rev. 0 | Page 16 of 36

There are six rules of reset.

Rule 1—on power up, keep the hard reset pin (RESET_B)

asserted.

Rule 2—if MCLK is unstable, keep the hard reset pin

(RESET_B) asserted.

Rule 3—after MCLK is stable, keep the hard reset pin

(RESET_B) asserted for at least 20 μs.

Rule 4—after the 20 μs of Rule 3 has elapsed, assert the error

reset bit (Bit 03 in Register 0x19).

Rule 5—the hard reset signal (RESET_B) can be asserted

asynchronously to MCLK, but upon deassertion, must make

setup and hold requirements upon the MCLK.

Rule 6—the minimum pulse width of RESET_B must be at least

three MCLK periods.

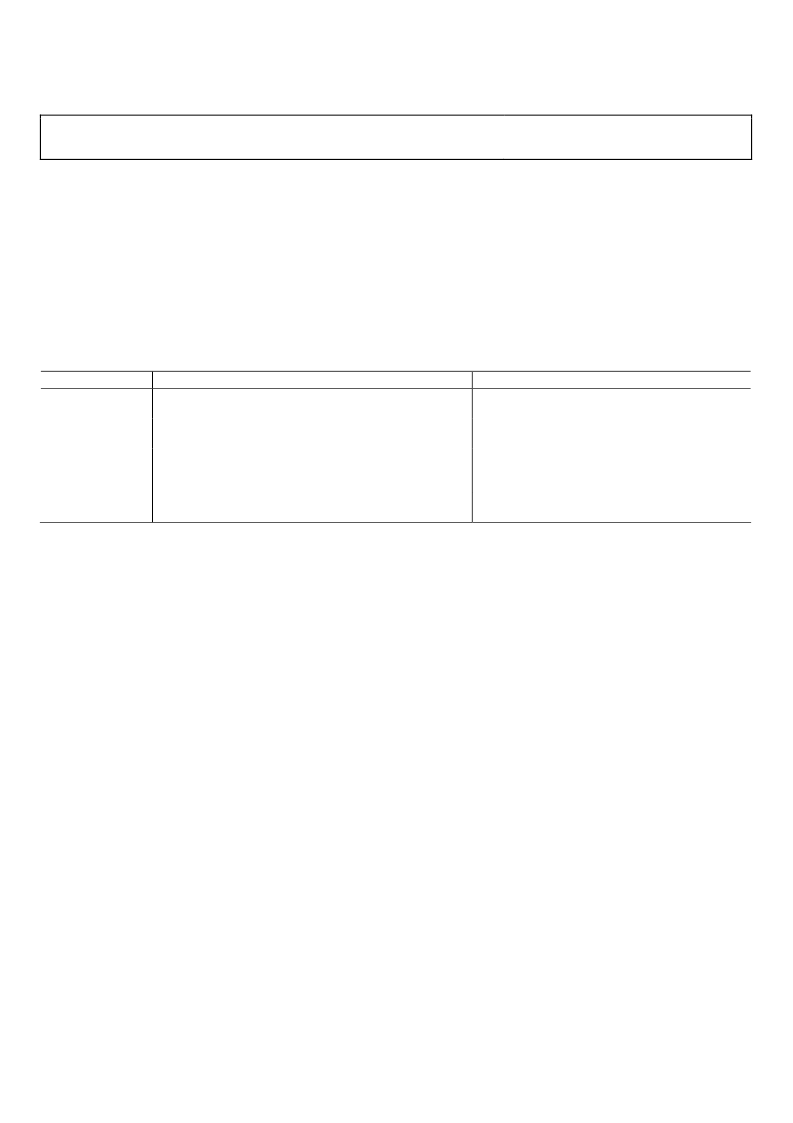

Table 11. Comparison Between Normal Mode and Clock Generation Mode

Normal Mode (CLKGEN_MD_EN=0)

Period Start

A single signal for all four channels, I_PER_EARLY_T0EN.

Clock Generator Mode(CLKGEN_MD_EN=1)

Four signals, one per channel; PAT_MASK[N] operates

as a period start signal for channel N.

Waveform memory location is fixed at Address 0.

Waveform

Memory Selection

Input Delay

Each channel N is selected via the I_PAT_PATDATA_N vector

every rising edge of I_MCLK.

A single vector adjust input delay for all channels,

INPUT_DELAY.

Four vectors are available, one per channel. For each

Channel N, PAT_PATDATA_N operates as

INPUT_DELAY for Channel N.

No masking of fail operations is available.

Fail Masking

Edge N for all channels can mask the fail operation every

rising edge of I_MCLK via PAT_MASK[N].

相關PDF資料 |

PDF描述 |

|---|---|

| ADATE207BBPZ | Quad Pin Timing Formatter |

| ADAU1401 | SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| ADAU1401YSTZ | SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| ADAU1401YSTZ-RL | SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| ADAU1513 | Class-D Audio Power Stage |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADATE207BBPZ | 功能描述:IC TIMING FORMATTER QUAD 256BGA RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:- 標準包裝:1 系列:- 類型:時鐘/頻率發生器,多路復用器 PLL:是 主要目的:存儲器,RDRAM 輸入:晶體 輸出:LVCMOS 電路數:1 比率 - 輸入:輸出:1:2 差分 - 輸入:輸出:無/是 頻率 - 最大:400MHz 電源電壓:3 V ~ 3.6 V 工作溫度:0°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:Digi-Reel® 其它名稱:296-6719-6 |

| ADATE209 | 制造商:AD 制造商全稱:Analog Devices 功能描述:4.0 Gbps Dual Driver |

| ADATE209BBCZ | 制造商:Analog Devices 功能描述:4.0 GBPS DUAL DRIVER - Rail/Tube |

| ADATE209BCPZ | 制造商:Analog Devices 功能描述: |

| ADATE302-02 | 制造商:AD 制造商全稱:Analog Devices 功能描述:500 MHz Dual Integrated DCL with Differential Drive/Receive, Level Setting DACs, and Per Pin PMU |

發布緊急采購,3分鐘左右您將得到回復。