- 您現在的位置:買賣IC網 > PDF目錄374033 > ADSP-21161N (Analog Devices, Inc.) DSP Microcomputer PDF資料下載

參數資料

| 型號: | ADSP-21161N |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 數字信號處理 |

| 英文描述: | DSP Microcomputer |

| 中文描述: | DSP微機 |

| 文件頁數: | 3/60頁 |

| 文件大小: | 1019K |

| 代理商: | ADSP-21161N |

第1頁第2頁當前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

–3–

REV. A

ADSP-21161N

TABLE OF CONTENTS

GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . 3

ADSP-21161N Family Core Architecture . . . . . . . . . 5

SIMD Computational Engine . . . . . . . . . . . . . . . . 5

Independent, Parallel Computation Units . . . . . . . 5

Data Register File . . . . . . . . . . . . . . . . . . . . . . . . . 5

Single-Cycle Fetch of Instruction and

Four Operands . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Instruction Cache . . . . . . . . . . . . . . . . . . . . . . . . . 5

Data Address Generators With Hardware Circular

Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Flexible Instruction Set . . . . . . . . . . . . . . . . . . . . . 5

ADSP-21161N Memory and I/O Interface Features . 5

Dual-Ported On-Chip Memory . . . . . . . . . . . . . . . 5

Off-Chip Memory and Peripherals Interface . . . . . 6

SDRAM Interface . . . . . . . . . . . . . . . . . . . . . . . . . 6

Target Board JTAG Emulator Connector . . . . . . . 7

DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Multiprocessing . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Link Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Serial Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Serial Peripheral (Compatible) Interface . . . . . . . . 9

Host Processor Interface . . . . . . . . . . . . . . . . . . . . 9

General-Purpose I/O Ports . . . . . . . . . . . . . . . . . . . 9

Program Booting . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Phase-Locked Loop and Crystal Double Enable . . 9

Power Supplies . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Development Tools . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Designing an Emulator-Compatible

DSP Board (Target) . . . . . . . . . . . . . . . . . . . . . 10

Additional Information . . . . . . . . . . . . . . . . . . . . . . 11

PIN FUNCTION DESCRIPTIONS . . . . . . . . . . . . . 12

BOOT MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . 18

ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . 19

ESD SENSITIVITY . . . . . . . . . . . . . . . . . . . . . . . . 19

TIMING SPECIFICATIONS . . . . . . . . . . . . . . . . 20

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . 21

Power-up Sequencing – Silicon

Revision 0.3, 1.0, 1.1 . . . . . . . . . . . . . . . . . . . . 22

Clock Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Clock Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Memory Read – Bus Master . . . . . . . . . . . . . . . . 27

Memory Write – Bus Master . . . . . . . . . . . . . . . . 28

Synchronous Read/Write – Bus Master . . . . . . . . 29

Synchronous Read/Write – Bus Slave . . . . . . . . . . 30

Host Bus Request . . . . . . . . . . . . . . . . . . . . . . . . 31

Asynchronous Read/Write –

Host to ADSP-21161N . . . . . . . . . . . . . . . . . . 33

Three-State Timing – Bus Master, Bus Slave . . . . 35

DMA Handshake . . . . . . . . . . . . . . . . . . . . . . . . 37

SDRAM Interface – Bus Master . . . . . . . . . . . . . 39

Link Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Serial Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

SPI Interface Specifications . . . . . . . . . . . . . . . . . 47

JTAG Test Access Port and Emulation . . . . . . . . 50

Output Drive Currents . . . . . . . . . . . . . . . . . . . . . . 51

Test Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Output Enable Time . . . . . . . . . . . . . . . . . . . . . . 51

Output Disable Time . . . . . . . . . . . . . . . . . . . . . 51

Example System Hold Time Calculation . . . . . . . 51

Capacitive Loading . . . . . . . . . . . . . . . . . . . . . . . 52

Environmental Conditions . . . . . . . . . . . . . . . . . . . 52

Thermal Characteristics . . . . . . . . . . . . . . . . . . . 52

225-BALL METRIC MBGA

PIN CONFIGURATIONS . . . . . . . . . . . . . . . . . . 53

OUTLINE DIMENSIONS . . . . . . . . . . . . . . . . . . . . 55

ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . 55

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

GENERAL DESCRIPTION

The ADSP-21161N SHARC DSP is the first low cost derivative

of the ADSP-21160 featuring Analog Devices Super Harvard

Architecture. Easing portability, the ADSP-21161N is source

code compatible with the ADSP-21160 and with first generation

ADSP-2106x SHARCs in SISD (Single Instruction, Single

Data) mode. Like other SHARC DSPs, the ADSP-21161N is a

32-bit processor that is optimized for high performance DSP

applications. The ADSP-21161N includes a 100 MHz core, a

dual-ported on-chip SRAM, an integrated I/O processor with

multiprocessing support, and multiple internal buses to eliminate

I/O bottlenecks.

As was first offered in the ADSP-21160, the ADSP-21161N

offers a Single-Instruction-Multiple-Data (SIMD) architecture.

Using two computational units (ADSP-2106x SHARCs have

one), the ADSP-21161N can double cycle performance versus

the ADSP-2106x on a range of DSP algorithms.

Fabricated in a state of the art, high speed, low power CMOS

process, the ADSP-21161N has a 10 ns instruction cycle time.

With its SIMD computational hardware running at 100 MHz,

the ADSP-21161N can perform 600 million math operations per

second.

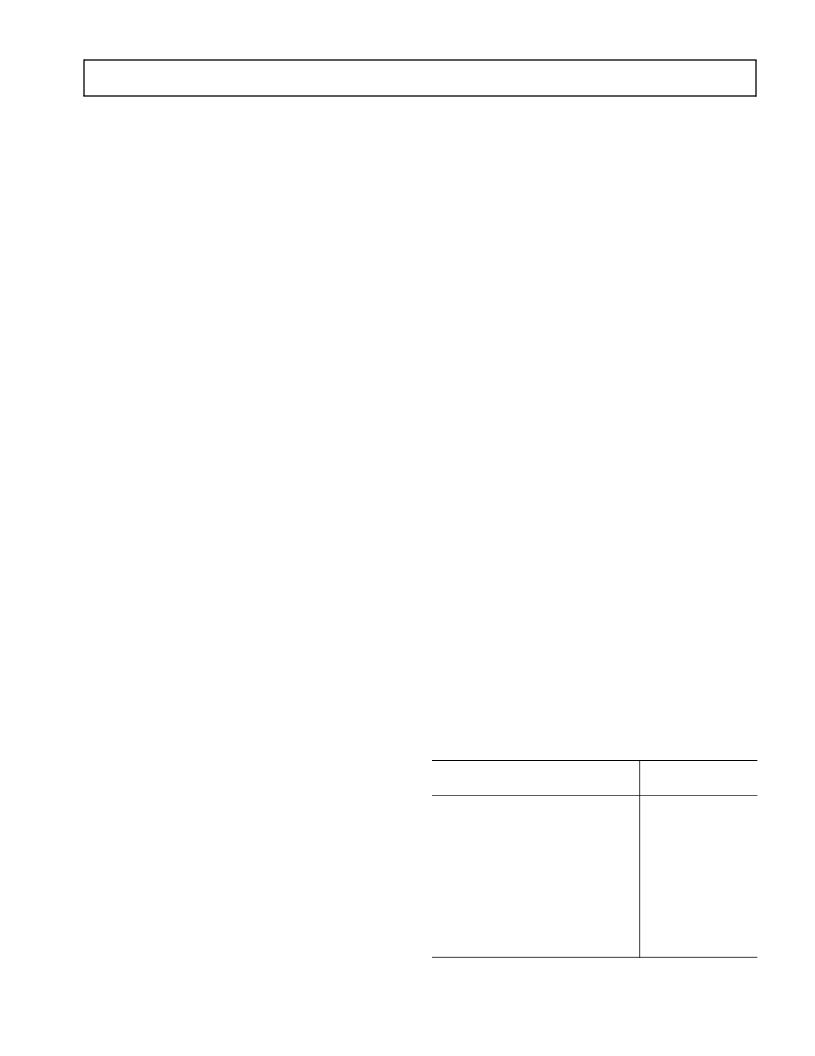

Table 1

shows performance benchmarks for the

ADSP-21161N.

Table 1. Benchmarks (at 100 MHz)

Benchmark Algorithm

Speed

(at 100 MHz)

1024 Point Complex FFT

(Radix 4, with reversal)

FIR Filter (per tap)

1

IIR Filter (per biquad)

1

Matrix Multiply (pipelined)

[3

×

3]

×

[3

×

1]

[4

×

4]

×

[4

×

1]

Divide (y/x)

Inverse Square Root

DMA Transfers

171 μs

5 ns

40 ns

1

1

Specified in SISD mode. Using SIMD, the same benchmark applies for

two sets of computations. For example, two sets of biquad operations can

be performed in the same amount of time as the SISD mode benchmark.

30 ns

37 ns

60 ns

1

40 ns

1

800 M bytes/s

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-21161NCCA-100 | DSP Microcomputer |

| ADSP-21161NKCA-100 | DSP Microcomputer |

| ADSP-21262SBBC-150 | Embedded Processor |

| ADSP-21262SBBCZ150 | Embedded Processor |

| ADSP-21262SKSTZ200 | SHARC Processor |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADSP-21161NCCA-100 | 功能描述:IC DSP CONTROLLER 32BIT 225MBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21161NCCAZ100 | 功能描述:IC DSP CONTROLLER 32BIT 225MBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21161NKCA-100 | 功能描述:IC DSP CONTROLLER 32BIT 225MBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21161NKCA-100Z | 制造商:Analog Devices 功能描述: |

| ADSP-21161NKCAZ100 | 功能描述:IC DSP CONTROLLER 32BIT 225MBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

發布緊急采購,3分鐘左右您將得到回復。