- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98215 > TFP420PAP (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP64 PDF資料下載

參數(shù)資料

| 型號(hào): | TFP420PAP |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| 封裝: | 10 X 10 MM, 1.40 MM HEIGHT, 0.50 MM PITCH, POWER, THERMALLY ENHANCED, PLASTIC, TQFP-64 |

| 文件頁(yè)數(shù): | 20/20頁(yè) |

| 文件大小: | 253K |

| 代理商: | TFP420PAP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)

TFP420

PanelBus

DIGITAL TRANSMITTER

SLDS123A – MARCH 2000 – REVISED JUNE 2000

9

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

functional description (continued)

hot plug/unplug (auto connect/disconnect detection)

The TFP420 supports hot plug/unplug (auto connect/disconnect detection) for the DVI link. The connection

status of DVI link and HTPLG sense terminal is provided by the CON_STATUS register. The RXCON bit

indicates if a DVI receiver is connected to the TXC+ and TXC–. HPCON bit reflects the current state of the

HTPLG terminal connected to the monitor via DVI connector. HTPLG terminal is 3-V tolerant with an internal

digital debouncing circuit to allow for direct connection to the DVI connector.

Whenever one or more connection status bits change states, the corresponding bit in the IN_STATUS bit is set

to 1 to record the changes. An interrupt can also be generated as an option. The interrupt for each type of

connect/disconnect event can be individually enabled or disabled by writing a 1 or 0 to the corresponding bit

in the INT_ENABLE register. Notice that INT_ENABLE register does not affect the state of the INT_STATUS

bits. A host can either poll the INT_STATUS bits or rely on the interrupt to learn about the states or the change

of states of the connections. The interrupt continues to be asserted until 1 is written to the corresponding

interrupt bit in the INT_STATUS register to reset the bit back to 0. Writing 0 to an interrupt status bit has no effect.

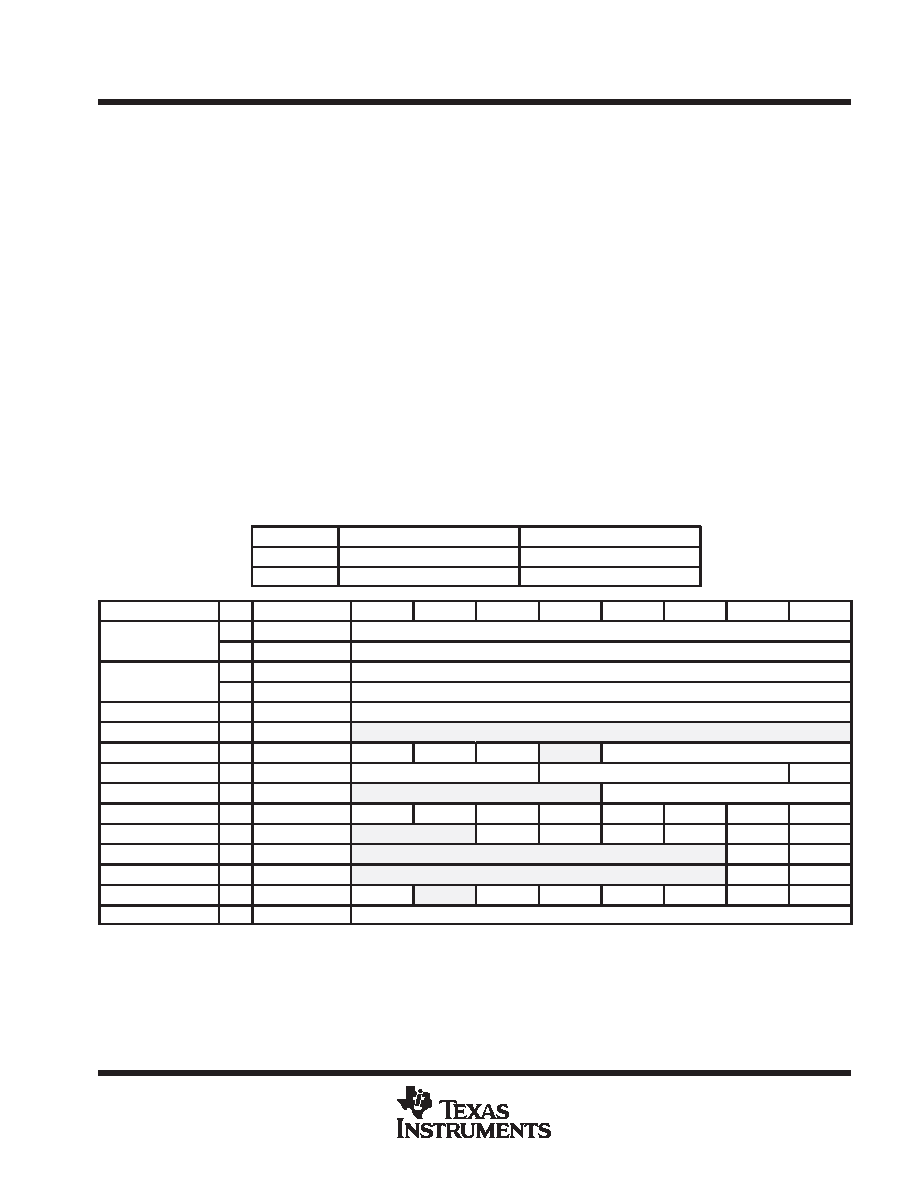

register map

The TFP420 is a standard I2C slave device. All the registers can be written and read through the I2C interface.

The I2C base address of the TFP420 is dependent on terminal 10 (A0) as shown in Table 1.

Table 1. Base I2C Address

Terminal 10

WRITE ADDRESS (HEX)

READ ADDRESS (HEX)

0

40

41

1

42

43

REGISTER

RW

SUBADDRESS

BIT7

BIT6

BIT5

BIT4

BIT3

BIT2

BIT1

BIT0

VEN ID

R

00

Ven_id[7:0]

VEN_ID

R

01

Ven_id[15:8]

DEV ID

R

02

Dev_Id[7:0]

DEV_ID

R

03

Dev_id[15:8]

REV_ID

R

04

Rev_Id[7:0]

RESERVED

05–39

RESERVED

F_CONTROL

RW

3A

Cbar

Intcko

RGBF

Fmt[3:0]

CLK_CTRL

RW

3B

Ckindsk[3:0]

Ckencse

VIDOUT_CTRL

RW

3C

Vidout[3:0]

SYNC_CTRL0

RW

3D

Syn_g

Fid_pol

Vs_fid

Hs_com

Vsen

Hsen

Tvsen

Thsen

CON_STATUS

R

3E

Daccon3

Daccon2

Daccon1

Daccon0

Hpcon

Rxcon

INT_STATUS

RW

3F

Hpevnt

Rxevnt

INT_ENABLE

RW

40

Hpen

Rxen

GP_CTRL

RW

41

Gio1_en

Gp1_in

Gp0_in

Gp1_oe

Gp0_oe

Gp1_out

Gp0_out

RESERVED

42–FF

RESERVED

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TFP501PZPG4 | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TFP501PZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TFP503PZPG4 | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TFP503PZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TFP510PAPG4 | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TFP424 | 制造商:Pentair Technical Products / Hoffman 功能描述:4 in Fan Package 24 VDC , 24vdc, |

| TFP42SS | 制造商:Pentair Technical Products / Hoffman 功能描述:230V,50/60Hz,16/14W,0.14/0.11A , 230v 50/60Hz, SS Type 304 |

| TFP42UL12 | 制造商:Pentair Technical Products / Hoffman 功能描述:230V,50/60Hz,16/14W,0.14/0.11A , 230v 50/60Hz, |

| TFP4N60 | 制造商:TAK_CHEONG 制造商全稱:Tak Cheong Electronics (Holdings) Co.,Ltd 功能描述:N-Channel Power MOSFET 4.1A, 600V, 2.5Ω |

| TFP4N65 | 制造商:TAK_CHEONG 制造商全稱:Tak Cheong Electronics (Holdings) Co.,Ltd 功能描述:N-Channel Power MOSFET 3.9A, 650V, 3.0Ω |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。