- 您現在的位置:買賣IC網 > PDF目錄98286 > TPS65820RSHTG4 (TEXAS INSTRUMENTS INC) 8-CHANNEL POWER SUPPLY SUPPORT CKT, PQCC56 PDF資料下載

參數資料

| 型號: | TPS65820RSHTG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 電源管理 |

| 英文描述: | 8-CHANNEL POWER SUPPLY SUPPORT CKT, PQCC56 |

| 封裝: | 7 X 7 MM, GREEN, PLASTIC, QFN-56 |

| 文件頁數: | 19/98頁 |

| 文件大小: | 2290K |

| 代理商: | TPS65820RSHTG4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁

SERIAL INTERFACE

Overview

Register Default Values

I2C Address

Incremental Read

I2C Bus Release

Sleep Mode Operation

I2C Bus Error Recovery

I2C Communication Protocol

SLVS663B – MAY 2006 – REVISED APRIL 2008 .............................................................................................................................................................. www.ti.com

The TPS65820 is compatible with a host-controlled environment, with internal parameters and status information

accessible via an I2C interface. An I2C communication port provides a simple way for an I2C compatible host to

access system status information and reset fault modes, functioning as a SLAVE port enabling I2C compatible

hosts to WRITE to or to READ from internal registers. The TPS65820 I2C port is a 2-wire bidirectional interface

using SCL (clock) and SDA (data) pins; the SDA pin is open drain and requires an external pullup. The I2C is

designed to operate at SCL frequencies up to 400 kHz. The standard 8 bit command is supported, the CMD part

of the sequence is the 8 bit register address to READ from or to WRITE to.

The internal TPS65820 registers are loaded during the initial power-up from an internal, non-volatile memory

bank. The power-up default values are described in the sections detailing the registers functionality.

The register contents remain intact as long as OUT pin voltage remains above the internal UVLO threshold,

VUVLO When the OUT pin voltage falls below the VUVLO threshold all register bits are reset to the internal power

up default.

The I2C specification contains several global addresses, which the slaves on the bus are required to respond to.

The TPS65820 only responds (ACK) to addresses: 0x90 and 0x91 and does not respond (NACK) to any other

address.

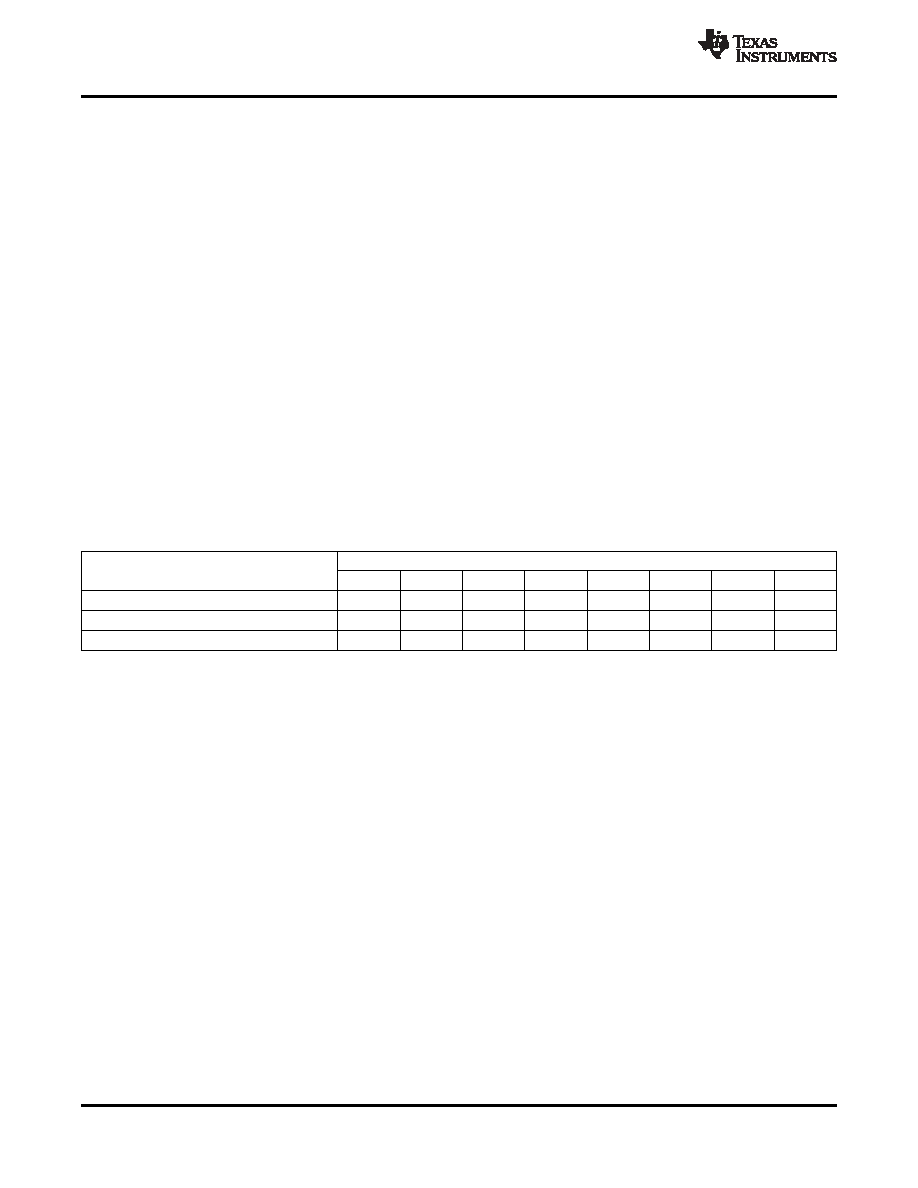

Table 1. TPS65820 I2C Read/Write Address

BYTE

BIT

MSB

6

5

4

3

2

1

LSB

TPS65820 I2C WRITE ADDRESS

1

0

1

0

TPS65820 I2C READ ADDRESS

1

0

1

0

1

I/O DATA BUS

B7

B6

B5

B4

B3

B2

B1

B0

The TPS65820 does not support incremental read operations. Each register must be accessed in a single read

operation.

The TPS65820 I2C engine does not create START or STOP states on the I2C bus during normal operation.

When the sleep mode is set SDAT is held LO by the TPS65820. The overall system operation is not affected, as

in sleep mode all TPS65820 integrated supplies are disabled and no power is available for any external devices

connected to the TPS65820 SDAT pin. When sleep mode ends the SDAT pin is released before the TPS65820

integrated regulated supplies are enabled. See section on System Sequencing and TPS65820 Operating Modes

for additional details on sleep mode operation.

The I2C bus specification does not define a method to be used when recovering from a host side bus error.

During a read operation the SDA pin can be left in a LO state if the host has not sent enough SCL pulses to

complete a transaction (i.e., host side bus error). The TPS65820 clears any SDA LO condition if 10 SCL pulses

are sent by the host, enabling recovery from host side bus error events.

The following conventions are used when describing the communication protocol:

26

Copyright 2006–2008, Texas Instruments Incorporated

Product Folder Link(s): TPS65820

相關PDF資料 |

PDF描述 |

|---|---|

| TPS65910RSLT | POWER SUPPLY SUPPORT CKT, PQCC48 |

| TPS65920A2ZCHR | SPECIALTY CONSUMER CIRCUIT, PBGA139 |

| TPS65920A2ZCH | SPECIALTY CONSUMER CIRCUIT, PBGA139 |

| TPS65920BZCHR | SPECIALTY CONSUMER CIRCUIT, PBGA139 |

| TPS65920BZCH | SPECIALTY CONSUMER CIRCUIT, PBGA139 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TPS658310YFFR | 功能描述:PMIC 解決方案 PMU w/Switching Chgr & Lighting Cntrl RoHS:否 制造商:Texas Instruments 安裝風格:SMD/SMT 封裝 / 箱體:QFN-24 封裝:Reel |

| TPS65835EVM-705 | 功能描述:電源管理IC開發工具 TPS65835 Eval Mod RoHS:否 制造商:Maxim Integrated 產品:Evaluation Kits 類型:Battery Management 工具用于評估:MAX17710GB 輸入電壓: 輸出電壓:1.8 V |

| TPS65835RKPR | 功能描述:PMIC 解決方案 Adv PMU w/Integrated MSP430 RoHS:否 制造商:Texas Instruments 安裝風格:SMD/SMT 封裝 / 箱體:QFN-24 封裝:Reel |

| TPS65835RKPT | 功能描述:PMIC 解決方案 ADVANCED PMU RoHS:否 制造商:Texas Instruments 安裝風格:SMD/SMT 封裝 / 箱體:QFN-24 封裝:Reel |

| TPS65851ZQZR | 制造商:Texas Instruments 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。