- 您現在的位置:買賣IC網 > PDF目錄373915 > AD7725 (Analog Devices, Inc.) 16-Bit 900 kSPS ADC with a Programmable Postprocessor PDF資料下載

參數資料

| 型號: | AD7725 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 16-Bit 900 kSPS ADC with a Programmable Postprocessor |

| 中文描述: | 16位900 ksps模數轉換器的可編程后處理器 |

| 文件頁數: | 18/28頁 |

| 文件大小: | 442K |

| 代理商: | AD7725 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

REV. A

–18–

AD7725

XTAL

MCLK

1M

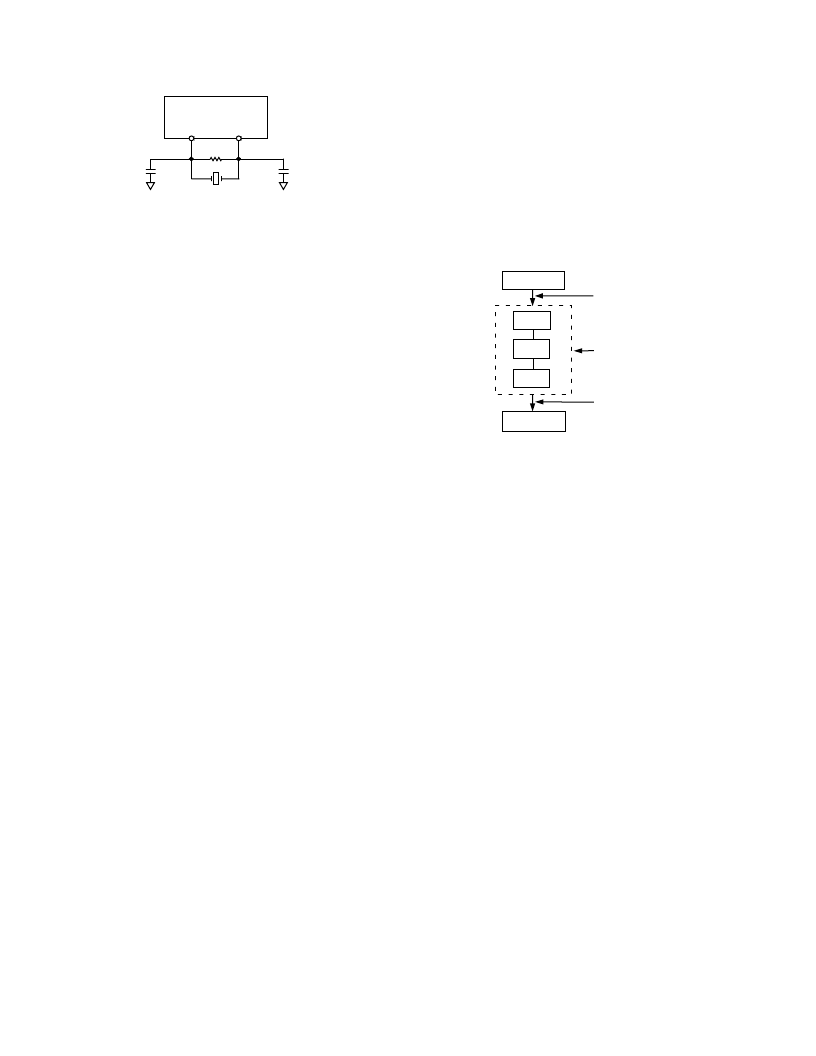

Figure 18. Crystal Oscillator Connection

When an external clock source is being used, the internal

oscil-

lator circuit can be disabled by tying XTAL_OFF high. A low

phase noise clock should be used to generate the ADC sam-

pling clock because sampling clock jitter effectively modulates

the input signal and raises the noise floor. The sampling

clock

generator should be isolated from noisy digital circuits, grounded,

and heavily decoupled to the analog ground plane.

The sampling clock generator should be referenced to the analog

ground in a split ground system; however, this is not always pos-

sible because of system constraints. In many applications, the

sampling clock must be derived from a higher frequency multi-

purpose system clock that is generated on the digital ground

plane. If the clock signal is passed between its origin on a digital

ground plane to the AD7725 on the analog ground plane, the

ground noise between the two planes adds directly to the clock

and will produce excess jitter. The jitter can cause degradation

in the signal-to-noise ratio and also produce unwanted harmon-

ics. This can be remedied somewhat by transmitting the sampling

signal as a differential one, using either a small RF transformer

or a high speed differential driver and a receiver such as PECL.

In either case, the original master system clock should be gener-

ated from a low phase noise crystal oscillator.

SYSTEM SYNCHRONIZATION

The SYNC input provides a synchronization function for use in

parallel or serial mode. SYNC allows the user to begin gathering

samples of the analog input from a known point in time.

This

allows a system using multiple AD7725s, operated from a

common master clock, to be synchronized so that each ADC

simultaneously updates its output register. In a system using

multiple AD7725s, a common signal to their SYNC inputs

will synchronize their operation. When SYNC is high, the digi-

tal filter sequencer is reset to zero. A SYNC pulse, one CLKIN

cycle long, can be applied. This way, SYNC is sensed

low on

the next rising edge of CLKIN. When SYNC is sensed low,

normal conversion continues. Following a SYNC, the

modula-

tor and filter need time to settle before data can be read from

the AD7725. Also, when INIT is taken high, it activates SYNC,

which ensures that multiple devices cascaded in serial mode will

sample their analog inputs simultaneously.

FILTERING

The Preset Filter

The preset filter is the digital filter directly following the modu-

lator. This is a fixed filter whose main function is to remove the

large out-of-band quantization noise shaped by the modulator.

This filter is made up of three cascaded half-band FIR filters,

and each filter decimates by two. The word rate into the preset

filter is CLKIN, and due to the decimation in the three subse-

quent filter stages, the output word rate of the preset filter, and

thus the input word rate to the postprocessor, is CLKIN/8. See

Figure 19.

POST-

PROCESSOR

MODULATOR

FIR 1

DEC 2

FIR 2

DEC 2

FIR 3

DEC 2

PRESET

FILTER

INPUT WORD

RATE = CLKIN

OUTPUT WORD

RATE = CLKIN/8

Figure 19. The Preset Filter

The Postprocessor

The AD7725 contains Systolix’s PulseDSP

mable postprocessor. The postprocessor directly follows the

preset filter. The postprocessor core is a systolic array of simple

high performance processors. These processors are grouped into

36 multiply accumulate (MAC) blocks, with each block consist-

ing of three multipliers and one adder. Each block can process

three filter taps, thus the postprocessor allows up to 36 3 = 108

filter taps. In a systolic array, numerical data is pumped around

processors. Each of these processors is allocated to a dedicated

function and only performs that single function. The data is

passed between processors and, in this manner, complex opera-

tions are performed on the input signal. In the AD7725, data

transfers between processors are fully synchronous. As a result,

the user does not have to consider timing issues.

The postprocessor core is optimized for signal conditioning

applications. In this type of application, generally the most

common function is filtering. The core can support any filter

structure, whether FIR, IIR, recursive, or nonrecursive. The

core also supports polynomial functions, commonly used in

linearization algorithms.

Data can be transparently decimated or interpolated when

passed between processors. This simplifies the design of multirate

filtering and gives great flexibility when specifying the final

output word rate. The AD7725 postprocessor supports decima-

tion/interpolation by factors up to 256.

TM

user-program-

相關PDF資料 |

PDF描述 |

|---|---|

| AD7725BS | 16-Bit 900 kSPS ADC with a Programmable Postprocessor |

| AD7729 | Dual Sigma-Delta ADC with Auxiliary DAC |

| AD7729AR | Dual Sigma-Delta ADC with Auxiliary DAC |

| AD7729ARU | Dual Sigma-Delta ADC with Auxiliary DAC |

| AD7730LBR | Bridge Transducer ADC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7725BS | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 900ksps 16-bit Parallel/Serial 44-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:16-BIT PROGRAMMABLE SIGMA-DELTA ADC I.C. - Bulk 制造商:Analog Devices 功能描述:IC 16BIT ADC SMD 7725 MQFP44 |

| AD7725BSC-REEL | 制造商:Analog Devices 功能描述: |

| AD7725BS-REEL | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 900ksps 16-bit Parallel/Serial 44-Pin MQFP T/R 制造商:Rochester Electronics LLC 功能描述:16-BIT PROGRAMMABLE SIGMA-DELTA ADC I.C. - Tape and Reel |

| AD7725BSZ | 功能描述:IC ADC 16BIT PROG 44MQFP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:2,500 系列:- 位數:12 采樣率(每秒):3M 數據接口:- 轉換器數目:- 功率耗散(最大):- 電壓電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 供應商設備封裝:SOT-23-6 包裝:帶卷 (TR) 輸入數目和類型:- |

| AD7727BCPZRL | 制造商:Analog Devices 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。