- 您現在的位置:買賣IC網 > PDF目錄373915 > AD7725 (Analog Devices, Inc.) 16-Bit 900 kSPS ADC with a Programmable Postprocessor PDF資料下載

參數資料

| 型號: | AD7725 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 16-Bit 900 kSPS ADC with a Programmable Postprocessor |

| 中文描述: | 16位900 ksps模數轉換器的可編程后處理器 |

| 文件頁數: | 20/28頁 |

| 文件大小: | 442K |

| 代理商: | AD7725 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

REV. A

–20–

AD7725

Filter Design

The bit stream of data from the modulator and preset filter is

available to the postprocessor at a frequency of CLKIN/8. Due

to the nature of the design of the postprocessor, there is an

unavoidable minimum decimate by 2 resulting in the maximum

output data rate of any filter being CLKIN/16.

A filter can be either FIR or IIR in design. FIR filters are inherently

stable and have linear phase. However, they are computationally

inefficient and require more coefficients for a given roll-off com-

pared to IIR filters. IIR filters have the disadvantage of being

potentially unstable and having nonlinear phase. The maximum

number of taps that the postprocessor can hold is 108. Therefore,

a single filter with 108 taps can be generated, or a multistage filter

can be designed whereby the total number of taps adds up to 108.

Design Factors

Stop-Band Attenuation and Transition Width

In filter design, it is desirable to have a large stop-band attenu-

ation and a narrow filter transition width. To achieve both of

these, a large number of filter taps is required. Therefore some

compromises have to be made during the design to be able to

optimize the amount of taps used. There is usually a trade-off of

stop-band attenuation for transition width, or vice versa. For

example, a filter with a cutoff frequency of 100 kHz that rolls off

between 100 kHz and 200 kHz uses fewer taps than a filter with a

cutoff frequency of 100 kHz that rolls off between 100 kHz and

150 kHz. To reduce the number of taps used to achieve a

certain specification, a multistage filter can be designed that

performs

decimation between stages. The first filter stage can be

used to perform decimation and as a prefilter to remove out-of-

band noise, then the subsequent stages can have more stringent

specifications.

Decimation

Decimation reduces the output data rate of the filter, resulting in

lower input data rates for subsequent filter stages.

When decimation

is used in a multistage filter, the noise is wrapped around f

S

/2 each

time the bit stream is decimated by 2. It is therefore important to

appropriately filter out the quantization noise that will wrap into

the band of interest when decimation occurs, prior to decimation.

With appropriate filtering, the noise floor will increase by 3 dB each

time the data stream is decimated by 2; however the noise floor is

down at 120 dB prior to decimation. Therefore, with suitable deci-

mation, the SNR will be 83 dB typically at the AD7725 output.

Decimating the data rate allows an improvement in the filter

transition width equal to the inverse of the decimation factor.

For FIR filters, if a filter is designed for an input data rate of

half the maximum data rate, i.e., the previous filter stage had

decimation by 2, the filter can obtain half the transition width of

a filter designed for the maximum input data rate for a given

number of taps. For example, the number of taps required to

generate a filter with a cutoff frequency of 100 kHz and a

stop-band frequency of 200 kHz will equal the number of taps

required to generate a filter with a cutoff frequency of 100 kHz

and a stop-band frequency of 150 kHz if the data stream is

decimated by 2 prior to the filtering stage. For IIR filters,

decimation has no effect on the transition width.

When decimation is performed, the amount of filter coefficients

required to achieve certain filter specifications is reduced, result-

ing in a reduction in the power dissipation of the device to

realize the filter. Therefore, if a one-stage filter meets the roll-off

and stop-band attenuation requirements of the application but

is dissipating more power than is acceptable, then decimation

will provide a solution here. Prior to decimating, a suggestion is

to use a half-band filter as these require a low number of taps to

accomplish simple low-pass filtering. A half-band filter has its

midpoint of the transition region centered on half the Nyquist

frequency (or f

S

/4). By decimating though, because the input to

subsequent stages is reduced, so is the bandwidth.

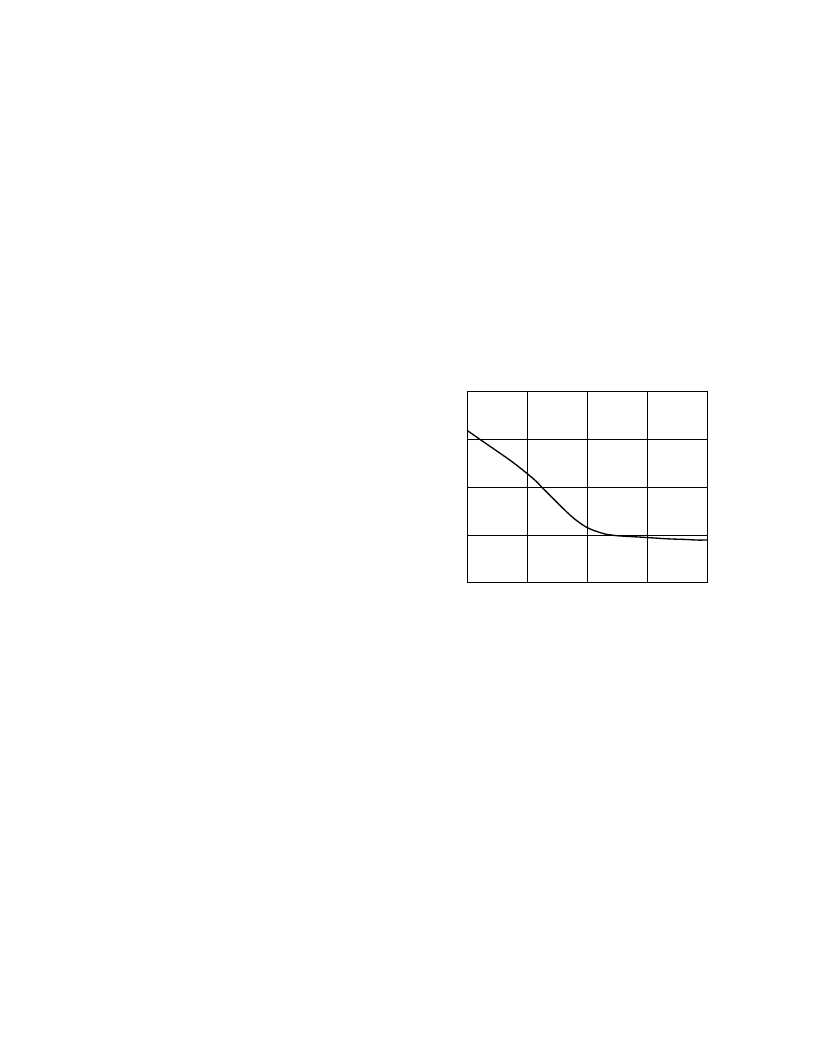

Figure 22 shows that for a given transition width, as the

decimation factor prior to the filter is increased the current

consumption is reduced, resulting in reduced power dissipation.

DECIMATION FACTOR

120

100

400

8

2

I

D

4

6

80

60

Figure 22. I

DD

vs. Decimation for a Filter with a

Transition Width of 66 kHz as Shown in Figure 1

Power Consumption vs. Filter Taps vs. CLKIN Frequency

When designing filters for the AD7725, an important factor to

take into account is the power consumption. There is a direct

relationship between DI

DD

, the number of filter taps used in

the postprocessor, and the CLKIN frequency. The maximum

I

DD

(combined AI

DD

and DI

DD

) allowed by the AD7725 pack-

age is 150 mA. The more filter taps used, the higher the DI

DD

.

Also, the higher the CLKIN frequency, the higher the DI

DD

.

Therefore, a trade-off sometimes needs to be made between

CLKIN frequency and filter taps to stay within the power

budget of the part.

These power constraints are built into the filter design package,

Filter Wizard. As the filter is being designed, the power con-

sumption is shown and is highlighted once the power budget

has been exceeded.

相關PDF資料 |

PDF描述 |

|---|---|

| AD7725BS | 16-Bit 900 kSPS ADC with a Programmable Postprocessor |

| AD7729 | Dual Sigma-Delta ADC with Auxiliary DAC |

| AD7729AR | Dual Sigma-Delta ADC with Auxiliary DAC |

| AD7729ARU | Dual Sigma-Delta ADC with Auxiliary DAC |

| AD7730LBR | Bridge Transducer ADC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7725BS | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 900ksps 16-bit Parallel/Serial 44-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:16-BIT PROGRAMMABLE SIGMA-DELTA ADC I.C. - Bulk 制造商:Analog Devices 功能描述:IC 16BIT ADC SMD 7725 MQFP44 |

| AD7725BSC-REEL | 制造商:Analog Devices 功能描述: |

| AD7725BS-REEL | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 900ksps 16-bit Parallel/Serial 44-Pin MQFP T/R 制造商:Rochester Electronics LLC 功能描述:16-BIT PROGRAMMABLE SIGMA-DELTA ADC I.C. - Tape and Reel |

| AD7725BSZ | 功能描述:IC ADC 16BIT PROG 44MQFP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:2,500 系列:- 位數:12 采樣率(每秒):3M 數據接口:- 轉換器數目:- 功率耗散(最大):- 電壓電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 供應商設備封裝:SOT-23-6 包裝:帶卷 (TR) 輸入數目和類型:- |

| AD7727BCPZRL | 制造商:Analog Devices 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。