- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373970 > AD9886KS-140 (ANALOG DEVICES INC) Analog Interface for Flat Panel Displays PDF資料下載

參數(shù)資料

| 型號(hào): | AD9886KS-140 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | Analog Interface for Flat Panel Displays |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP160 |

| 封裝: | PLASTIC, MQFP-160 |

| 文件頁(yè)數(shù): | 24/32頁(yè) |

| 文件大小: | 248K |

| 代理商: | AD9886KS-140 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)當(dāng)前第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)

REV. 0

AD9886

–24–

0E

4

One bit that determines the polarity of the HSYNC out-

put and the SOG output. Table XI shows the effect of this

option. SYNC indicates the logic state of the sync pulse.

HSYNC Output Polarity

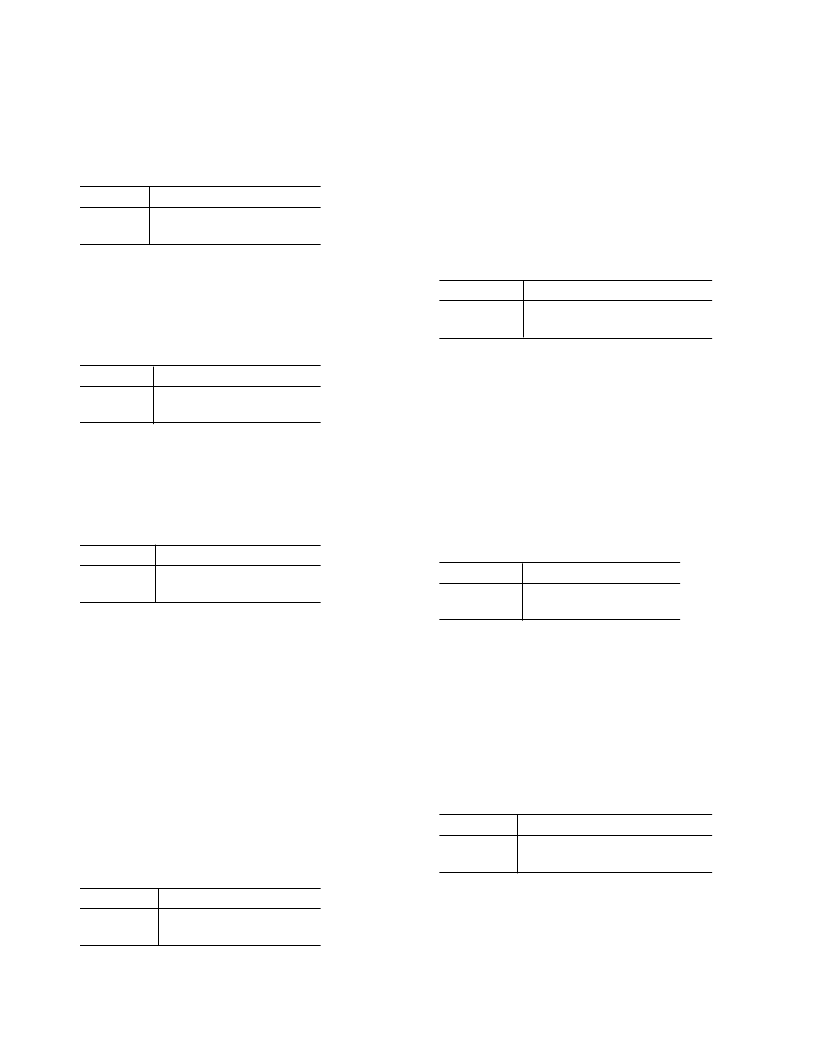

Table XI. HSYNC Output Polarity Settings

Setting

SYNC

0

1

Logic 1 (Positive Polarity)

Logic 0 (Negative Polarity)

The default setting for this register is 1. (This option

works on both the analog and digital interfaces.)

3

VSYNC Output Invert

One bit that inverts the polarity of the VSYNC output.

Table XII shows the effect of this option.

0E

Table XII. VSYNC Output Polarity Settings

Setting

VSYNC Output

0

1

No Invert

Invert

The default setting for this register is 1. (This option

works on both the analog and digital interfaces.)

0F

7

A bit that must be set to indicate the polarity of the HSYNC

signal that is applied to the PLL HSYNC input.

HSPOL HSYNC Input Polarity

Table XIII. HSYNC Input Polarity Settings

HSPOL

Function

0

1

Active LOW

Active HIGH

Active LOW is the traditional negative-going Hsync pulse.

All timing is based on the leading edge of Hsync, which is

the FALLING edge. The rising edge has no effect.

Active HIGH is inverted from the traditional Hsync, with

a positive-going pulse. This means that timing will be

based on the leading edge of Hsync, which is now the

RISING edge.

The device will operate if this bit is set incorrectly, but the

internally generated clamp position, as established by

CLPOS, will not be placed as expected, which may gener-

ate clamping errors.

The power-up default value is HSPOL = 1.

6 COAST Input Polarity

A bit to indicate the polarity of the COAST signal that is

applied to the PLL COAST input.

0F

Table XIV. COAST Input Polarity Settings

CSTPOL

Function

0

1

Active LOW

Active HIGH

Active LOW means that the clock generator will ignore

Hsync inputs when COAST is LOW, and continue oper-

ating at the same nominal frequency until COAST goes

HIGH.

Active HIGH means that the clock generator will ignore

Hsync inputs when COAST is HIGH, and continue oper-

ating at the same nominal frequency until COAST goes

LOW.

This function needs to be used along with the COAST

polarity override bit (Register 14, Bit 1).

The power-up default value is CSTPOL = 1.

5 Clamp Input Signal Source

A bit that determines the source of clamp timing.

0F

Table XV. Clamp Input Signal Source Settings

EXTCLMP

Function

0

1

Internally-Generated Clamp

Externally-Provided Clamp Signal

A 0 enables the clamp timing circuitry controlled by

CLPLACE and CLDUR. The clamp position and dura-

tion is counted from the leading edge of Hsync.

A 1 enables the external CLAMP input pin. The three

channels are clamped when the CLAMP signal is

active. The polarity of CLAMP is determined by the

CLAMPOL bit.

The power-up default value is EXTCLMP = 0.

4

CLAMP Input Signal Polarity

A bit that determines the polarity of the externally pro-

vided CLAMP signal.

0F

Table XVI. CLAMP Input Signal Polarity Settings

EXTCLMP

Function

0

1

Active LOW

Active HIGH

A Logic 0 means that the circuit will clamp when CLAMP

is HIGH, and it will pass the signal to the ADC when

CLAMP is LOW.

A Logic 1 means that the circuit will clamp when CLAMP

is LOW, and it will pass the signal to the ADC when

CLAMP is HIGH.

The power-up default value is CLAMPOL = 1.

3 External Clock Select

A bit that determines the source of the pixel clock.

0F

Table XVII. External Clock Select Settings

EXTCLK

Function

0

1

Internally Generated Clock

Externally Provided Clock Signal

A Logic 0 enables the internal PLL that generates the

pixel clock from an externally provided Hsync.

A Logic 1 enables the external CKEXT input pin. In this

mode, the PLL Divide Ratio (PLLDIV) is ignored. The

clock phase adjust (PHASE) is still functional.

The power-up default value is EXTCLK = 0.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9898 | CCD Signal Processor with Precision Timing⑩ Generator |

| AD9898KCP-20 | CCD Signal Processor with Precision Timing⑩ Generator |

| AD9898KCPRL-20 | TVPS00RF-21-41S W/ PC CON |

| AD9901 | Ultrahigh Speed Phase/Frequency Discriminator |

| AD9901KP | Ultrahigh Speed Phase/Frequency Discriminator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9887 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Dual Interface for Flat Panel Displays |

| AD9887/PCB | 制造商:Analog Devices 功能描述:INTRFC DUAL FOR FLAT PNL DISPLAYS 160MQFP - Bulk |

| AD9887A | 制造商:AD 制造商全稱:Analog Devices 功能描述:Dual Interface for Flat Panel Displays |

| AD9887A/PCB | 制造商:Analog Devices 功能描述:INTRFC FOR FLAT PNL DISPLAY 16SOIC W - Bulk |

| AD9887AKS-100 | 制造商:Analog Devices 功能描述:Interface for Flat Panel Display 160-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:DUAL A/D INTERFACE FOR FLAT PANEL - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。