- 您現在的位置:買賣IC網 > PDF目錄373973 > AD9992BBCZ (ANALOG DEVICES INC) 12-Bit CCD Signal Processor with Precision Timing Generator PDF資料下載

參數資料

| 型號: | AD9992BBCZ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費家電 |

| 英文描述: | 12-Bit CCD Signal Processor with Precision Timing Generator |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PBGA105 |

| 封裝: | 8 X 8 MM, 0.65 MM PITCH, ROHS COMPLIANT, MO-225, CSPBGA-105 |

| 文件頁數: | 87/92頁 |

| 文件大小: | 718K |

| 代理商: | AD9992BBCZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁當前第87頁第88頁第89頁第90頁第91頁第92頁

AD9992

Rev. 0 | Page 87 of 92

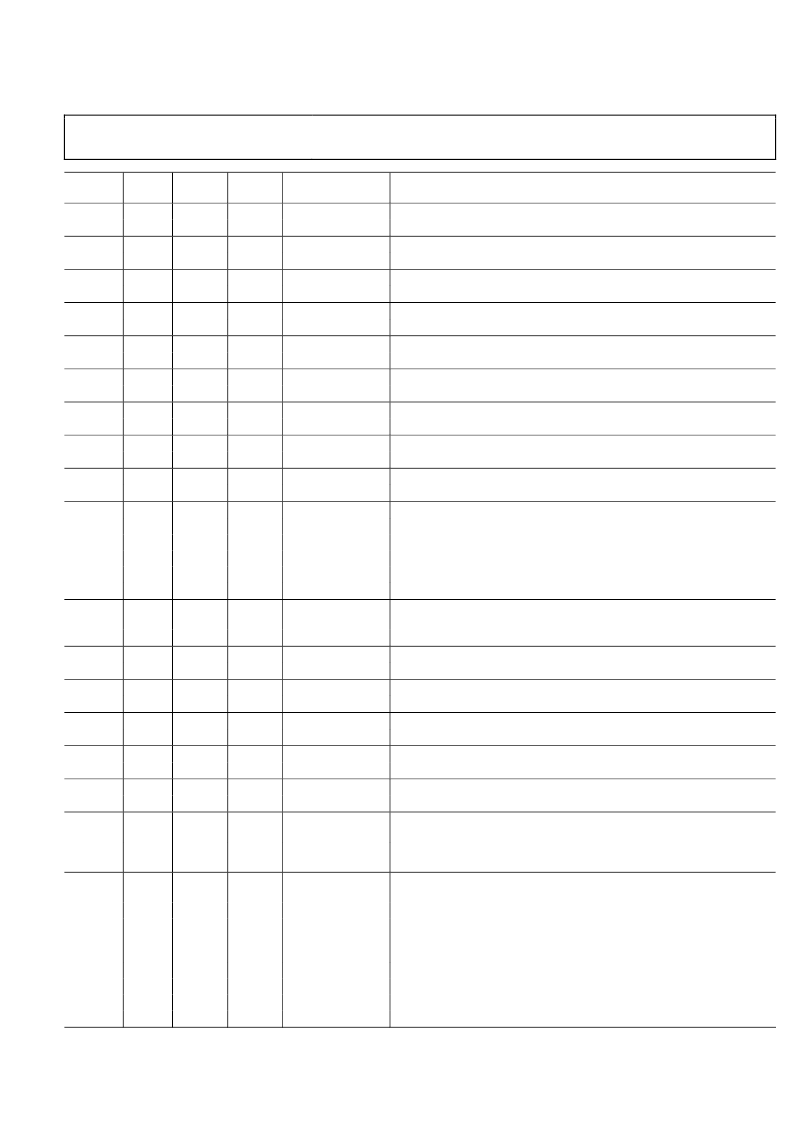

Address

0F

10

11

12

13

14

15

16

17

18

19

Data

Bits

[12:0]

[25:13]

[12:0]

[25:13]

[12:0]

[25:13]

[12:0]

[25:13]

[12:0]

[25:13]

[12:0]

[25:13]

[12:0]

[25:13]

[12:0]

[25:13]

[12:0]

[25:13]

[12:0]

[20:13]

[21]

[22]

[23]

[25:24]

[12:0]

Default

Value

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

Update

Type

SCP

SCP

SCP

SCP

SCP

SCP

SCP

SCP

SCP

SCP

SCP

Name

VSTARTC

VLENC

VREPC_ODD

VREPC_EVEN

VSTARTD

VLEND

VREPD_ODD

VREPD_EVEN

FREEZE1

RESUME1

FREEZE2

RESUME2

FREEZE3

RESUME3

FREEZE4

RESUME4

HBLKSTART

HBLKEND

HBLKLEN

HBLKREP

HBLKMASK_H1

HBLKMASK_H2

HBLKMASK_HL

TEST

HBLKTOGO1

Description

Start position of selected V-Pattern Group C.

Length of selected V-Pattern Group C.

Number of repetitions for V-Pattern Group C for odd lines.

Number of repetitions for V-Pattern Group C for even lines.

Start position of selected V-Pattern Group D.

Length of selected V-Pattern Group D.

Number of repetitions for V-Pattern Group D for odd lines.

Number of repetitions for V-Pattern Group D for even lines.

Holds the V-outputs at their current levels.

Resumes the operation of V-outputs to finish the pattern.

Holds the V-outputs at their current levels.

Resumes the operation of V-outputs to finish the pattern.

Holds the V-outputs at their current levels.

Resumes the operation of V-outputs to finish the pattern.

Holds the V-outputs at their current levels.

Resumes the operation of V-outputs to finish the pattern.

Start location for HBLK in HBLK Modes 1 and 2.

End location for HBLK in HBLK Modes 1 and 2.

HBLK length in HBLK Modes 1 and 2.

Number of HBLK repetitions in HBLK Modes 1 and 2.

Masking polarity for H1/H3/H5/H7 during HBLK.

Masking polarity for H2/H4/H6/H8 during HBLK.

Masking polarity for HL during HBLK.

Test use only. Set to 0.

First HBLK toggle position for odd lines, or RA0H1REPABC in HBLK Mode 2

(see HBLK Mode 2 Operation for more information).

Second HBLK toggle position for odd lines, or RA1H1REPABC.

Third HBLK toggle position for odd lines, or RA2H1REPABC.

Fourth HBLK toggle position for odd lines, or RA3H1REPABC.

Fifth HBLK toggle position for odd lines, or RA4H1REPABC.

Sixth HBLK toggle position for odd lines, or RA5H1REPABC.

First HBLK toggle position for even lines, or RA0H2REPABC.

Second HBLK toggle position for even lines, or RA1H2REPABC.

Third HBLK toggle position for even lines, or RA2H2REPABC.

Fourth HBLK toggle position for even lines, or RA3H2REPABC.

Fifth HBLK toggle position for even lines, or RA4H2REPABC.

Sixth HBLK toggle position for even lines, or RA5H2REPABC.

HBLK Repeat Area Start Position A for HBLK Mode 2. Set to 8191 if not

used.

HBLK Repeat Area Start Position B for HBLK Mode 2. Set to 8191 if not

used.

HBLK Repeat Area Start Position C for HBLK Mode 2. Set to 8191 if not

used.

Special V-sequence alternation enable.

1= enables operation of VALTSEL0_EVEN/ODD, VALTSEL1_EVEN/ODD

registers in FREEZE/RESUME registers. Must be enabled if special VALT

mode is used.

1 = enables use of special vertical pattern insertion into VPATA sequence.

[0]: use VPATB as the special pattern.

[1]: use VPATC as the special pattern.

[2]: use VPATD as the special pattern.

1A

1B

1C

1D

1E

1F

[25:13]

[12:0]

[25:13]

[12:0]

[25:13]

[12:0]

[25:13]

[12:0]

[25:13]

[12:0]

[25:13]

[12:0]

X

X

X

X

X

X

X

X

X

X

X

X

SCP

SCP

SCP

SCP

SCP

SCP

HBLKTOGO2

HBLKTOGO3

HBLKTOGO4

HBLKTOGO5

HBLKTOGO6

HBLKTOGE1

HBLKTOGE2

HBLKTOGE3

HBLKTOGE4

HBLKTOGE5

HBLKTOGE6

HBLKSTARTA

[25:13]

X

HBLKSTARTB

20

[12:0]

X

SCP

HBLKSTARTC

[13]

[14]

X

X

VSEQALT_EN

VALT_MAP

[17:15]

X

SPC_PAT_EN

相關PDF資料 |

PDF描述 |

|---|---|

| AD9992BBCZRL | 12-Bit CCD Signal Processor with Precision Timing Generator |

| AD9995KCP | 12-Bit CCD Signal Processor with Precision Timing ⑩ Generator |

| AD9995KCPRL | 12-Bit CCD Signal Processor with Precision Timing ⑩ Generator |

| AD9995 | 12-Bit CCD Signal Processor with Precision Timing ⑩ Generator |

| ADA4000-2ARMZ-RL | Low Cost, Precision JFET Input Operational Amplifiers |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9992BBCZRL | 功能描述:IC CCD SGNL PROC 12BIT 105CSPBGA RoHS:是 類別:集成電路 (IC) >> 接口 - 傳感器和探測器接口 系列:- 其它有關文件:Automotive Product Guide 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:74 系列:- 類型:觸控式傳感器 輸入類型:數字 輸出類型:數字 接口:JTAG,串行 電流 - 電源:100µA 安裝類型:表面貼裝 封裝/外殼:20-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:20-TSSOP 包裝:管件 |

| AD9993BBCZ | 功能描述:IC MIXED-SIGNAL FRONT END 196BGA 制造商:analog devices inc. 系列:- 包裝:托盤 零件狀態:在售 類型:ADC,DAC 輸入類型:LVDS 輸出類型:LVDS 接口:SPI 電流 - 電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:196-LFBGA,CSPBGA 供應商器件封裝:196-CSPBGA(12x12) 標準包裝:1 |

| AD9993BBCZRL | 功能描述:IC MIXED-SIGNAL FRONT END 196BGA 制造商:analog devices inc. 系列:- 包裝:帶卷(TR) 零件狀態:在售 類型:ADC,DAC 輸入類型:LVDS 輸出類型:LVDS 接口:SPI 電流 - 電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:196-LFBGA,CSPBGA 供應商器件封裝:196-CSPBGA(12x12) 標準包裝:1,500 |

| AD9993-EBZ | 功能描述:EVAL BOARD MXFE AD9993 制造商:analog devices inc. 系列:* 零件狀態:在售 標準包裝:1 |

| AD9994 | 制造商:AD 制造商全稱:Analog Devices 功能描述:12-Bit CCD Signal Processor with Precision Timing Generator |

發布緊急采購,3分鐘左右您將得到回復。