- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373975 > ADAU1702JSTZ-RL (ANALOG DEVICES INC) SigmaDSP 28-56-Bit Audio Processor with Two ADCs and Four DACs PDF資料下載

參數(shù)資料

| 型號: | ADAU1702JSTZ-RL |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費家電 |

| 英文描述: | SigmaDSP 28-56-Bit Audio Processor with Two ADCs and Four DACs |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| 封裝: | ROHS COMPLIANT, PLASTIC, MS-026BBC, LQFP-48 |

| 文件頁數(shù): | 28/52頁 |

| 文件大小: | 773K |

| 代理商: | ADAU1702JSTZ-RL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

ADAU1702

SIGNAL PROCESSING

The ADAU1702 is designed to provide all audio signal processing

functions commonly used in stereo or multichannel playback

systems. The signal processing flow is designed using the

SigmaStudio software, which allows graphical entry and real-

time control of all signal processing functions.

Many of the signal processing functions are coded using full,

56-bit, double-precision arithmetic data. The input and output

word lengths of the DSP core are 24 bits. Four extra headroom

bits are used in the processor to allow internal gains of up to

24 dB without clipping. Additional gains can be achieved by

initially scaling down the input signal in the DSP signal flow.

NUMERIC FORMATS

DSP systems commonly use a standard numeric format.

Fractional number systems are specified by an A.B format,

where A is the number of bits to the left of the decimal point

and B is the number of bits to the right of the decimal point.

The ADAU1702 uses the same numeric format for both the

parameter and data values. The format is as follows.

Numerical Format: 5.23

Linear range: 16.0 to (+16.0 1 LSB)

Examples:

1000 0000 0000 0000 0000 0000 0000 = 16.0

1110 0000 0000 0000 0000 0000 0000 = 4.0

1111 1000 0000 0000 0000 0000 0000 = 1.0

1111 1110 0000 0000 0000 0000 0000 = 0.25

1111 1111 0011 0011 0011 0011 0011 = 0.1

1111 1111 1111 1111 1111 1111 1111 = (1 LSB below 0.0)

0000 0000 0000 0000 0000 0000 0000 = 0.0

0000 0000 1100 1100 1100 1100 1101 = 0.1

0000 0010 0000 0000 0000 0000 0000 = 0.25

0000 1000 0000 0000 0000 0000 0000 = 1.0

0010 0000 0000 0000 0000 0000 0000 = 4.0

0111 1111 1111 1111 1111 1111 1111 = (16.0 1 LSB).

The serial port accepts up to 24 bits on the input and is sign-

extended to the full 28 bits of the DSP core. This allows internal

gains of up to 24 dB without internal clipping.

A digital clipper circuit is used between the output of the DSP

core and the DACs or serial port outputs (see Figure 28). This

clips the top four bits of the signal to produce a 24-bit output

Rev. 0 | Page 28 of 52

with a range of 1.0 (minus 1 LSB) to 1.0. Figure 28 shows the

maximum signal levels at each point in the data flow in both

binary and decibel levels.

4-BIT SIGN EXTENSION

DATA IN

1.23

(1.23

1.23

(0dB)

5.23

(24dB)

5.23

(24dB)

SERIAL

PORT

SIGNAL

PROCESSING

(5.23 FORMAT)

DIGITAL

CLIPPER

0

Figure 28. Numeric Precision and Clipping Structure

PROGRAMMING

On power-up, the ADAU1702 default program passes the

unprocessed input signals to the outputs (shown in Figure 13),

but the outputs are muted by default (see the Power-Up Sequence

section). There are 512 instruction cycles per audio sample,

resulting in about 25 MIPS available. The SigmaDSP runs in a

stream-oriented manner, meaning that all 512 instructions are

executed each sample period. The ADAU1702 can also be set

up to accept double- or quad-speed inputs by reducing the

number of instructions per sample that are set in the core

control register.

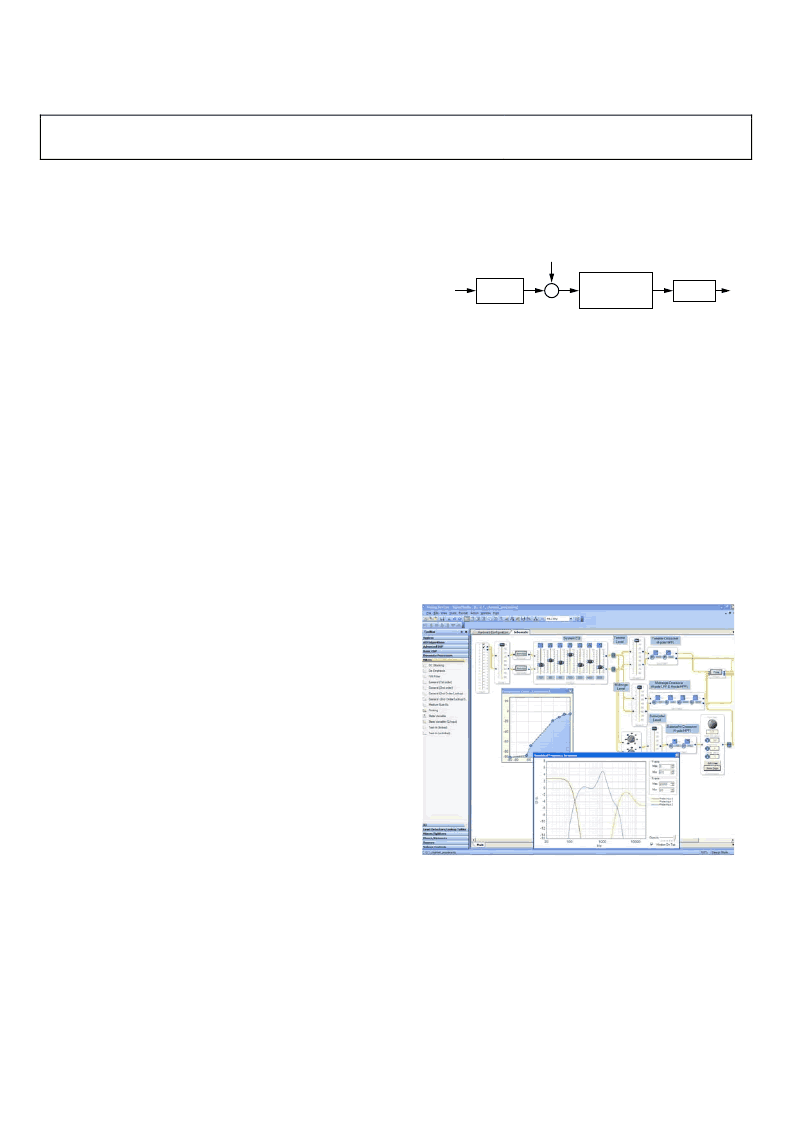

The part can be programmed easily using SigmaStudio (Figure 29),

a graphical tool provided by Analog Devices. No knowledge of

writing line-level DSP code is required. More information about

SigmaStudio can be found at

www.analog.com

.

0

Figure 29. SigmaStudio Screen Shot

相關PDF資料 |

PDF描述 |

|---|---|

| ADC912A | CMOS Microprocessor-Compatible 12-Bit A/D Converter |

| ADC912AFP | CMOS Microprocessor-Compatible 12-Bit A/D Converter |

| ADC912AFS | CMOS Microprocessor-Compatible 12-Bit A/D Converter |

| ADCMP341 | Dual 0.275% Comparators and Reference with Programmable Hysteresis |

| ADCMP341_07 | Dual 0.275% Comparators and Reference with Programmable Hysteresis |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ADAU1761 | 制造商:AD 制造商全稱:Analog Devices 功能描述:SigmaDSP Stereo, Low Power, 96 kHz, 24-Bit Audio Codec with Integrated PLL |

| ADAU1761BCPZ | 功能描述:IC SIGMADSP CODEC PLL 32LFCSP RoHS:是 類別:集成電路 (IC) >> 接口 - 編解碼器 系列:SigmaDSP® 標準包裝:2,500 系列:- 類型:PCM 數(shù)據(jù)接口:PCM 音頻接口 分辨率(位):15 b ADC / DAC 數(shù)量:1 / 1 三角積分調變:是 S/N 比,標準 ADC / DAC (db):- 動態(tài)范圍,標準 ADC / DAC (db):- 電壓 - 電源,模擬:2.7 V ~ 3.3 V 電壓 - 電源,數(shù)字:2.7 V ~ 3.3 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:80-VFBGA 供應商設備封裝:80-BGA MICROSTAR JUNIOR(5x5) 包裝:帶卷 (TR) 其它名稱:296-21257-2 |

| ADAU1761BCPZ | 制造商:Analog Devices 功能描述:IC, AUDIO CODEC, 24BIT, 96KHZ, LFCSP-32 |

| ADAU1761BCPZ-R7 | 功能描述:IC SIGMADSP CODEC PLL 32LFCSP RoHS:是 類別:集成電路 (IC) >> 接口 - 編解碼器 系列:SigmaDSP® 標準包裝:2,500 系列:- 類型:立體聲音頻 數(shù)據(jù)接口:串行 分辨率(位):18 b ADC / DAC 數(shù)量:2 / 2 三角積分調變:是 S/N 比,標準 ADC / DAC (db):81.5 / 88 動態(tài)范圍,標準 ADC / DAC (db):82 / 87.5 電壓 - 電源,模擬:2.6 V ~ 3.3 V 電壓 - 電源,數(shù)字:1.7 V ~ 3.3 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-WFQFN 裸露焊盤 供應商設備封裝:48-TQFN-EP(7x7) 包裝:帶卷 (TR) |

| ADAU1761BCPZ-RL | 功能描述:IC SIGMADSP CODEC PLL 32LFCSP RoHS:是 類別:集成電路 (IC) >> 接口 - 編解碼器 系列:SigmaDSP® 標準包裝:2,500 系列:- 類型:立體聲音頻 數(shù)據(jù)接口:串行 分辨率(位):18 b ADC / DAC 數(shù)量:2 / 2 三角積分調變:是 S/N 比,標準 ADC / DAC (db):81.5 / 88 動態(tài)范圍,標準 ADC / DAC (db):82 / 87.5 電壓 - 電源,模擬:2.6 V ~ 3.3 V 電壓 - 電源,數(shù)字:1.7 V ~ 3.3 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-WFQFN 裸露焊盤 供應商設備封裝:48-TQFN-EP(7x7) 包裝:帶卷 (TR) |

發(fā)布緊急采購,3分鐘左右您將得到回復。