- 您現在的位置:買賣IC網 > PDF目錄382356 > N643GT7MI (Advanced Micro Devices, Inc.) 64 Megabit (4 M x 16-Bit) CMOS 1.8 Volt-only Simultaneous Read/Write, Burst Mode Flash Memory PDF資料下載

參數資料

| 型號: | N643GT7MI |

| 廠商: | Advanced Micro Devices, Inc. |

| 英文描述: | 64 Megabit (4 M x 16-Bit) CMOS 1.8 Volt-only Simultaneous Read/Write, Burst Mode Flash Memory |

| 中文描述: | 64兆位(4個M x 16位)的CMOS 1.8伏,只有同時讀/寫,突發模式閃存 |

| 文件頁數: | 24/49頁 |

| 文件大小: | 382K |

| 代理商: | N643GT7MI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

22

Am29BDS643G

25692A2 May 8, 2006

D A T A S H E E T

the sector address. The device ID is read in three

cycles.

The system must write the reset command to return to

the read mode (or erase-suspend-read mode if the

bank was previously in Erase Suspend).

Program Command Sequence

Programming is a four-bus-cycle operation. The

program command sequence is initiated by writing two

unlock write cycles, followed by the program set-up

command. The program address and data are written

next, which in turn initiate the Embedded Program

algorithm. The system is

not

required to provide further

controls or timings. The device automatically provides

internally generated program pulses and verifies the

programmed cell margin. Table 10 shows the address

and data requirements for the program command

sequence.

When the Embedded Program algorithm is complete,

that bank then returns to the read mode and addresses

are no longer latched. The system can determine the

status of the program operation by monitoring DQ7 or

DQ6/DQ2. Refer to the Write Operation Status section

for information on these status bits.

Any commands written to the device during the

Embedded Program Algorithm are ignored.

Note that a

hardware reset

immediately terminates the program

operation. The program command sequence should be

reinitiated once that bank has returned to the read

mode, to ensure data integrity.

Programming is allowed in any sequence and across

sector boundaries.

A bit cannot be programmed

from “0” back to a “1.”

Attempting to do so may

cause that bank to set DQ5 = 1, or cause the DQ7 and

DQ6 status bit to indicate the operation was suc-

cessful. However, a succeeding read will show that the

data is still “0.” Only erase operations can convert a “0”

to a “1.”

Unlock Bypass Command Sequence

The unlock bypass feature allows the system to prima-

rily program to a bank faster than using the standard

program command sequence. The unlock bypass

command sequence is initiated by first writing two

unlock cycles. This is followed by a third write cycle

containing the unlock bypass command, 20h. That

bank then enters the unlock bypass mode. A two-cycle

unlock bypass program command sequence is all that

is required to program in this mode. The first cycle in

this sequence contains the unlock bypass program

command, A0h; the second cycle contains the program

address and data. Additional data is programmed in

the same manner. This mode dispenses with the initial

two unlock cycles required in the standard program

command sequence, resulting in faster total program-

ming time. Table 10 shows the requirements for the

unlock bypass command sequences.

During the unlock bypass mode, only the Unlock

Bypass Program and Unlock Bypass Reset commands

are valid. To exit the unlock bypass mode, the system

must issue the two-cycle unlock bypass reset

command sequence. The first cycle must contain the

bank address and the data 90h. The second cycle

need only contain the data 00h. The bank then returns

to the read mode.

The device offers accelerated program operations

through the V

PP

input. When the system asserts V

PP

on this input, the device automatically enters the

Unlock Bypass mode. The system may then write the

two-cycle Unlock Bypass program command

sequence. The device uses the higher voltage on the

V

PP

input to accelerate the operation.

Figure 1 illustrates the algorithm for the program oper-

ation. Refer to the Erase/Program Operations table in

the AC Characteristics section for parameters, and

Figure 13 for timing diagrams.

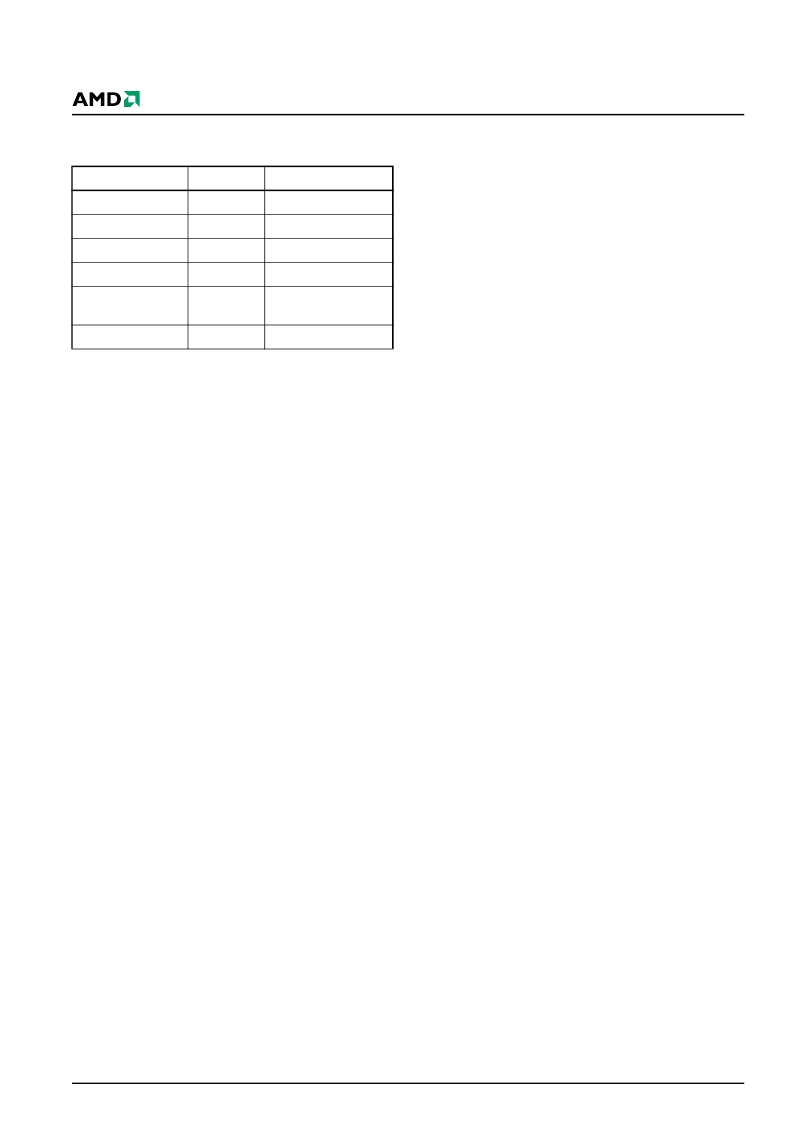

Description

Address

Read Data

Manufacturer ID

(BA) + 00h

0001h

Device ID, Word 1

(BA) + 01h

227Eh

Device ID, Word 2

(BA) + 0Eh

2202h

Device ID, Word 3

(BA) + 0Fh

2200h

Sector Block

Lock/Unlock

(SA) + 02h

0001 (locked),

0000 (unlocked)

Handshaking

(BA) + 03h

43h

相關PDF資料 |

PDF描述 |

|---|---|

| N80186 | High Integration 16-Bit Microprocessor iAPX86 Family |

| N80186-10 | High Integration 16-Bit Microprocessor iAPX86 Family |

| N80186-10B | High Integration 16-Bit Microprocessor iAPX86 Family |

| N80186B | High Integration 16-Bit Microprocessor iAPX86 Family |

| N80188 | High Integration 8-Bit Microprocessor |

相關代理商/技術參數 |

參數描述 |

|---|---|

| N6455A | 制造商:Agilent Technologies 功能描述:HARD COPY MANUAL, 4000X-SERIES OSCILLOSCOPE; Plug Type:-; Accessory Type:Hard Copy Manual; For Use With:InfiniiVision 4000 X-Series Oscilloscopes ;RoHS Compliant: NA |

| N6456A | 制造商:AGILENT TECHNOLOGIES, INC. 功能描述:Rackmount Kit for 2000 and 3000X Series Oscilloscopes 制造商:Agilent Technologies 功能描述:Bulk 制造商:Agilent Technologies 功能描述:OPTION RACK MOUNT KIT FOR X-SERIES 制造商:Agilent Technologies 功能描述:RACK MOUNT KIT; Accessory Type:Rackmount Kit; For Use With:Agilent InfiniiVision 2000X / 3000X Series Oscilloscopes ;RoHS Compliant: NA 制造商:Agilent Technologies 功能描述:Rack mount kit |

| N6457A | 制造商:AGILENT TECHNOLOGIES, INC. 功能描述:Soft Carrying Case and Front Panel Cover for 2000 and 3000X Series Scopes 制造商:Agilent Technologies 功能描述:Bulk 制造商:Agilent Technologies 功能描述:ACCESSORY SOFT CASE AND FRONT PANEL 制造商:Agilent Technologies 功能描述:ACCESSORY, SOFT CASE AND FRONT PANEL 制造商:Agilent Technologies 功能描述:SOFT CARRYING CASE AND FRONT PANEL COVER; Accessory Type:Case and Front Panel Cover; For Use With:Agilent InfiniiVision 2000X / 3000X Series Oscilloscopes ;RoHS Compliant: NA 制造商:Agilent Technologies 功能描述:Soft Carrying Case |

| N6458A-ABA | 制造商:Agilent Technologies 功能描述:Hard Copy User's Manual 2000 X series 制造商:Agilent Technologies 功能描述:N6458A / English Users Guide |

| N6459A-ABA | 制造商:Agilent Technologies 功能描述:Hard Copy Users Manual for 3000 X- Series Oscilliscope |

發布緊急采購,3分鐘左右您將得到回復。