- 您現在的位置:買賣IC網 > PDF目錄373914 > AD7713SQ (ANALOG DEVICES INC) LC2MOS Loop-Powered Signal Conditioning ADC PDF資料下載

參數資料

| 型號: | AD7713SQ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | LC2MOS Loop-Powered Signal Conditioning ADC |

| 中文描述: | 3-CH 24-BIT DELTA-SIGMA ADC, SERIAL ACCESS, CDIP24 |

| 封裝: | 0.300 INCH, HERMETIC SEALED, CERDIP-24 |

| 文件頁數: | 4/28頁 |

| 文件大小: | 516K |

| 代理商: | AD7713SQ |

第1頁第2頁第3頁當前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

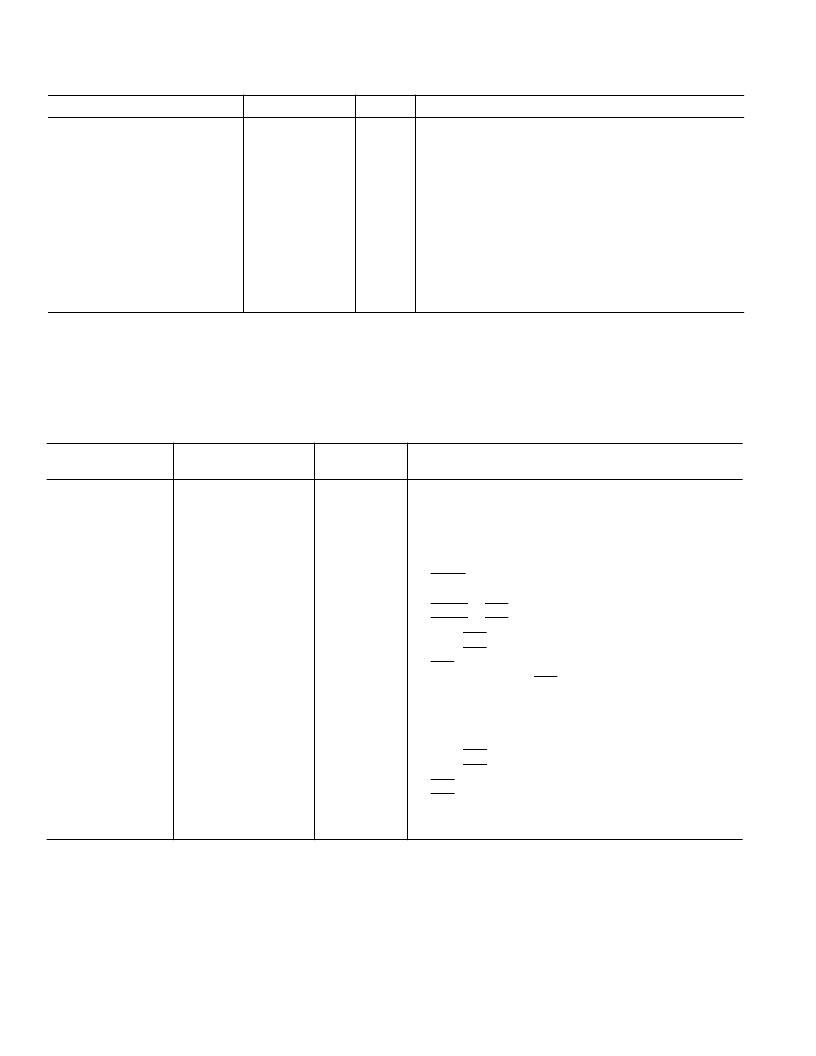

Parameter

A, S Versions

1

Units

Conditions/Comments

POWER REQUIREMENTS

Power Supply Voltages

AV

DD

Voltage

DV

DD

Voltage

16

Power Supply Currents

AV

DD

Current

+5 to +10

+5

V nom

V nom

±

5% for Specified Performance

±

5% for Specified Performance

0.6

0.7

0.5

1

mA max

mA max

mA max

mA max

AV

DD

= +5 V

AV

DD

= +10 V

f

CLK IN

= 1 MHz. Digital Inputs 0 V to DV

DD

f

CLK IN

= 2 MHz. Digital Inputs 0 V to DV

DD

Rejection w.r.t. AGND

DV

DD

Current

Power Supply Rejection

17

(AV

DD

and DV

DD

)

Power Dissipation

Normal Mode

Standby (Power-Down) Mode

See Note 18

dB typ

5.5

300

mW max

μ

W max

AV

DD

= DV

DD

= +5 V, f

CLK IN

= 1 MHz; Typically 3.5 mW

AV

DD

= DV

DD

= +5 V, Typically 150

μ

W

NOTES

16

The

±

5% tolerance on the DV

DD

input is allowed provided that DV

DD

does not exceed AV

DD

by more than 0.3 V.

17

Measured at dc and applies in the selected passband. PSRR at 50 Hz will exceed 120 dB with filter notches of 2 Hz, 5 Hz, 10 Hz, 25 Hz or 50 Hz. PSRR at 60 Hz

will exceed 120 dB with filter notches of 2 Hz, 6 Hz, 10 Hz, 30 Hz or 60 Hz.

18

PSRR depends on gain: gain of 1 = 70 dB typ; gain of 2 = 75 dB typ; gain of 4 = 80 dB typ; gains of 8 to 128 = 85 dB typ.

Specifications subject to change without notice.

AD7713–SPECIFICATIONS

REV. C

–4–

TIMING CHARACTERISTICS

1, 2

Limit at T

MIN

, T

MAX

(A, S Versions)

Parameter

Units

Conditions/Comments

f

CLK IN3, 4

400

2

0.4

×

t

CLK IN

0.4

×

t

CLK IN

50

50

1000

kHz min

MHz max

ns min

ns min

ns max

ns max

ns min

Master Clock Frequency: Crystal Oscillator or

Externally Supplied for Specified Performance

Master Clock Input Low Time; t

CLK IN

= 1/f

CLK IN

Master Clock Input High Time

Digital Output Rise Time; Typically 20 ns

Digital Output Fall Time; Typically 20 ns

SYNC

Pulse Width

t

CLK IN LO

t

CLK IN HI

t

r5

t

f5

t

1

Self-Clocking Mode

t

2

t

3

t

4

t

5

t

6

t

76

t

86

0

0

2

×

t

CLK IN

0

4

×

t

CLK IN

+ 20

4

×

t

CLK IN

+20

t

CLK IN

/2

t

CLK IN

/2

+ 30

t

CLK IN

/2

3

t

CLK IN

/2

50

0

4

×

t

CLK IN

+ 20

4

×

t

CLK IN

0

10

ns min

ns min

ns min

ns min

ns max

ns max

ns min

ns max

ns nom

ns nom

ns min

ns min

ns max

ns min

ns min

ns min

DRDY

to

RFS

Setup Time

DRDY

to

RFS

Hold Time

A0 to

RFS

Setup Time

A0 to

RFS

Hold Time

RFS

Low to SCLK Falling Edge

Data Access Time (

RFS

Low to Data Valid)

SCLK Falling Edge to Data Valid Delay

t

9

t

10

t

14

t

15

t

16

t

17

t

18

t

19

SCLK High Pulse Width

SCLK Low Pulse Width

A0 to

TFS

Setup Time

A0 to

TFS

Hold Time

TFS

to SCLK Falling Edge Delay Time

TFS

to SCLK Falling Edge Hold Time

Data Valid to SCLK Setup Time

Data Valid to SCLK Hold Time

(DV

DD

= +5 V

±

5%; AV

DD

= +5 V or +10 V

±

5%; AGND = DGND = 0 V; f

CLKIN

=2 MHz;

Input Logic 0 = 0 V, Logic 1 = DV

DD

unless otherwise noted.)

相關PDF資料 |

PDF描述 |

|---|---|

| AD7713 | Loop-Powered Signal Conditioning ADC(循環驅動LC2MOS信號調節A/D轉換器) |

| AD7714AN-3 | VARISTOR 30VRMS 0805 SMD |

| AD7714AN-5 | VARISTOR 40VRMS 1206 SMD |

| AD7714YRU | 3 V/5 V, CMOS, 500 uA Signal Conditioning ADC |

| AD7714* | 3 V/5 V. CMOS. 500 uA Signal Conditioning ADC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7714 | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V/5 V, CMOS, 500 uA Signal Conditioning ADC |

| AD7714ACHIPS-3 | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V/5 V, CMOS, 500 uA Signal Conditioning ADC |

| AD7714ACHIPS-5 | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V/5 V, CMOS, 500 uA Signal Conditioning ADC |

| AD7714AN-3 | 制造商:Rochester Electronics LLC 功能描述:24-BIT SIGMA DELTA A/D IC - Bulk 制造商:Analog Devices 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。