- 您現在的位置:買賣IC網 > PDF目錄365968 > TSB14AA1I FPGA (Field-Programmable Gate Array) PDF資料下載

參數資料

| 型號: | TSB14AA1I |

| 英文描述: | FPGA (Field-Programmable Gate Array) |

| 中文描述: | 電信提供商/數據通信 |

| 文件頁數: | 31/35頁 |

| 文件大小: | 224K |

| 代理商: | TSB14AA1I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當前第31頁第32頁第33頁第34頁第35頁

6

–

11

6.3.3

Arbitration Sequence Format

The following format for the arbitration sequence is used:

PRIORITY

ARBITRATION NUMBER

4-bits

6-bits

Each module on the backplane has unique 6-bit arbitration number that is equal to the nodes Physical_ID.

The arbitration number is preceded by four bits of priority. The MSB of the priority field is transmitted first.

The LSB of the priority field is followed by the MSB of the arbitration number.

Dynamic assignment of priority is accommodated.

The lowest priority level (all zeroes) is reserved for fair arbitration, and the highest priority level (all ones)

is reserved for the identification of the cycle start packet.

6.4

Arbitration

Unless a node is using immediate arbitration to access the bus (in which case there is no contention for the bus), it

is possible that more than one node can attempt to access the bus at a given time. Consequently, it is necessary for

a node to arbitrate for the bus in order to gain access to the bus.

NOTE:

A node uses immediate arbitration to send an acknowledge. Since there is no

contention for the bus in this case, arbitration is not necessary. A node that is transmitting an

acknowledge does not arbitrate for the bus, but merely waits for an acknowledge gap to be

detected before it begins transmission. If a node is attempting to gain access to the bus without

using immediate access, it must first arbitrate for the bus.

Arbitration occurs in response to a PHY arbitration request from the link. Nodes begin arbitrating once the bus has

become idle for a predetermined amount of time (the appropriate gap indication occurs). Once this happens, nodes

begin a bit-by-bit transmission of their arbitration sequence.

A node can obtain access to the bus in a limited number of ways. Since some arbitration classes allow nodes to begin

arbitration before others, nodes arbitrating with certain arbitration classes can detect that the bus is busy before they

can begin to arbitrate. In this way, certain arbitration classes can be bypassed, e.g., fair and urgent nodes do not get

a chance to arbitrate when another node is sending an acknowledge.

The backplane environment supports the fair, urgent, and immediate arbitration classes.

6.4.1

Fairness Intervals

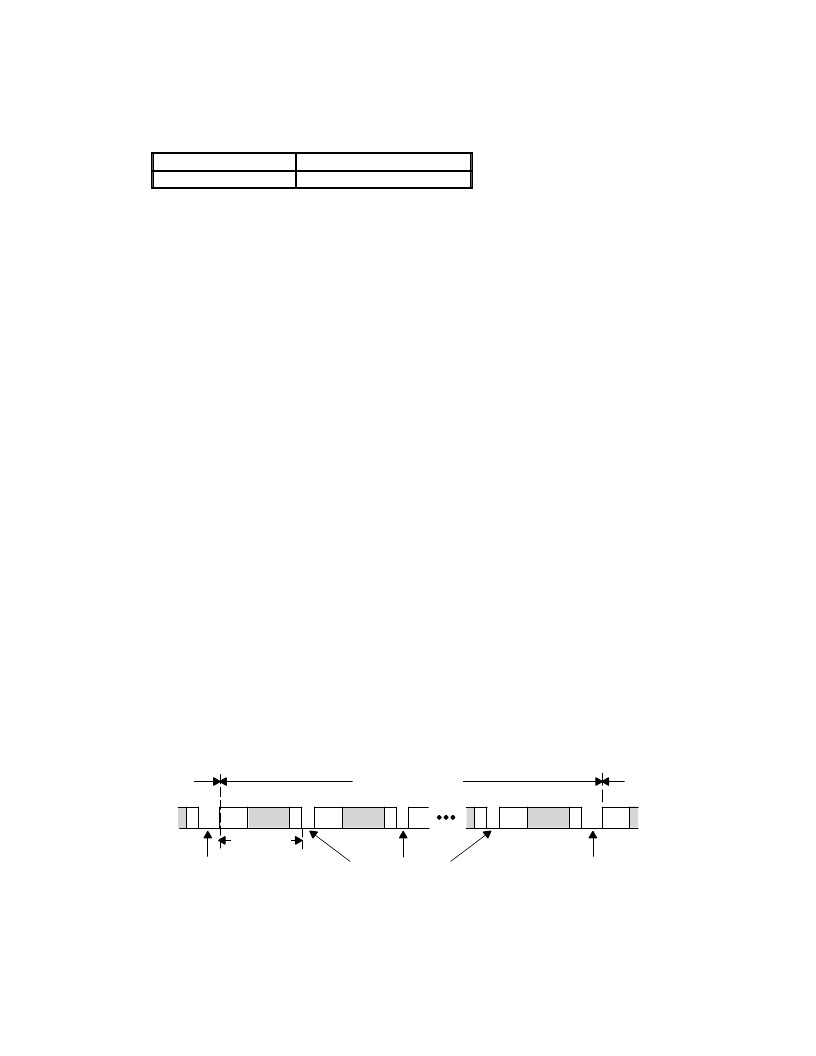

The fairness protocol is based on the concept of a fairness interval. A fairness interval consists of one or more periods

of bus activity separated by short idle periods called subaction gaps and is followed by a longer idle period known

as an arbitration reset gap. At the end of each gap, bus arbitration is used to determine the next bus owner. This

concept is shown in Figure 6

–

9.

arb

data

a

a

arb

data

a

arb

a

arb

data

a

arb

Owner A

Owner B

Owner M

Fairness Interval N

Fairness

Interval N

–

1

Fairness

Interval N+1

Subaction Gaps

Arbitration

Reset Gap

Arbitration

Reset Gap

Subaction

Figure 6

–

9. Fairness Interval

The implementation of the fair arbitration protocol is defined in terms of these fairness intervals as is discussed in

the following paragraphs.

相關PDF資料 |

PDF描述 |

|---|---|

| TSB14AA1T | FPGA (Field-Programmable Gate Array) |

| TSB14C01MHV | IC APEX 20KE FPGA 160K 484-FBGA |

| TSB14C01HV | 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB21LV03MHV | IC APEX 20KE FPGA 200K 484-FBGA |

| TSB21LV03CHV | IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TSB14AA1PFB | 功能描述:1394 接口集成電路 3.3V 1-port 50/100 Mbps Backplane PHY RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB14AA1PFBG4 | 功能描述:1394 接口集成電路 3.3V 1-port 50/100 Mbps Backplane PHY RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB14AA1T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecomm/Datacomm |

| TSB14AA1TPFB | 功能描述:IC BACKPLANE PHY 3.3V 48-TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標準包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應商設備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| TSB14C01 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

發布緊急采購,3分鐘左右您將得到回復。