- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365968 > TSB14AA1I FPGA (Field-Programmable Gate Array) PDF資料下載

參數(shù)資料

| 型號: | TSB14AA1I |

| 英文描述: | FPGA (Field-Programmable Gate Array) |

| 中文描述: | 電信提供商/數(shù)據(jù)通信 |

| 文件頁數(shù): | 32/35頁 |

| 文件大小: | 224K |

| 代理商: | TSB14AA1I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當前第32頁第33頁第34頁第35頁

6

–

12

6.4.2

Fair Arbitration

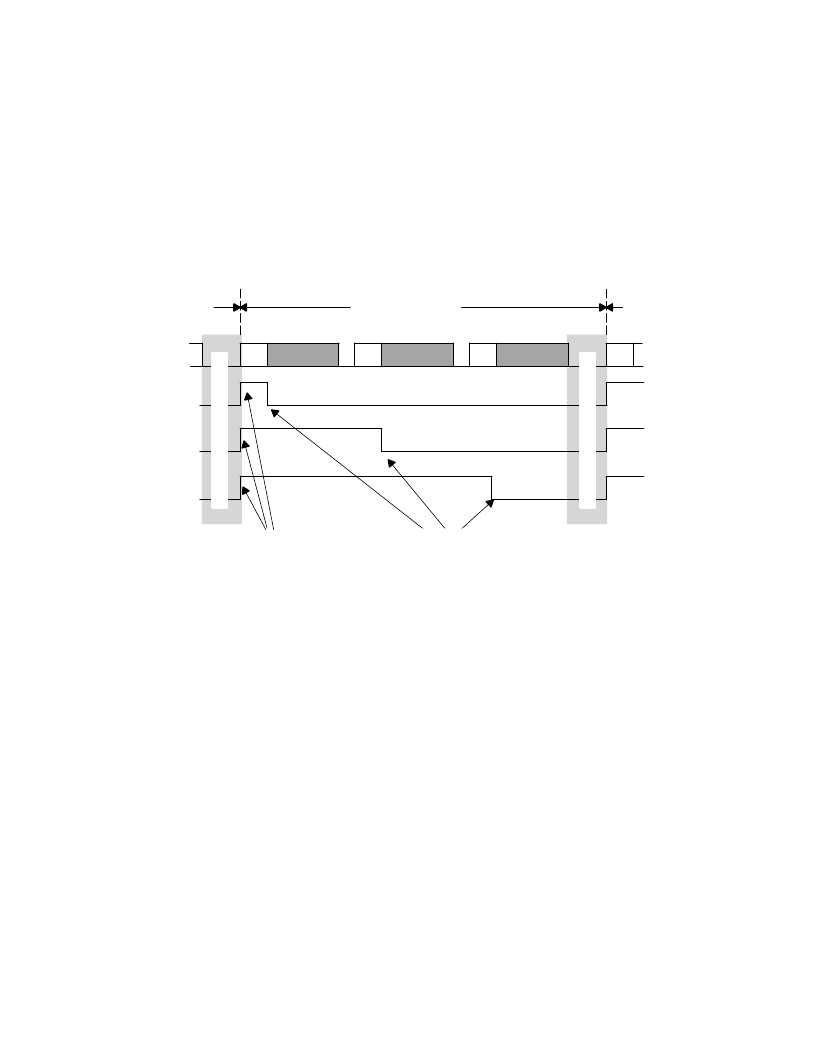

When using this arbitration class, an active node can send an asynchronous packet exactly once each fairness

interval. Once a subaction gap is detected, a node can begin arbitration when its Arbitration_Enable signal is set. The

Arbitration_Enable signal is set at the beginning of the fairness interval and is cleared when the node successfully

accesses the bus through fair arbitration. This disables further fair arbitration attempts by that node for the remainder

of the fairness interval. In the absence of urgent nodes, a fairness interval ends once all of the nodes attempting fair

arbitration have successfully accessed the bus. At this time, all of the fair nodes have their Arbitration_Enable signals

reset and cannot arbitrate for the bus. The bus remains idle until an arbitration reset gap occurs. Once this happens,

the next fairness interval begins. All of the nodes set their Arbitration_Enable signal and can begin to arbitrate for the

bus. This process is illustrated in Figure 6

–

10.

arb

arb

arb

arb

Node A

Node B

Node C

Clear When Node Wins Arbitration

Set at Arbitration Reset Gap

Note: Arbitration Number of A > B > C

Fairness Interval N

Fairness

Interval N

–

1

Fairness

Interval N+1

Node A

Node B

Node B

A

A

A

Figure 6

–

10. Fair Arbitration Timing

NOTE:

A node sending a concatenated subaction does not reset its Arbitration_Enable bit.

6.4.3

Urgent Arbitration

The backplane environment enhances the fair priority algorithm by splitting access opportunities among nodes based

on two priority classes: fair and urgent. Nodes using an urgent priority can use up to three-fourths of the access

opportunities, with the remaining equally shared among nodes using the fair priority. All nodes are required to

implement the fair priority class, while the urgent priority class is optional. Packets are labeled as urgent when that

priority class is used.

The fair/urgent allocation uses the same fairness interval described in fair arbitration but accompanies the

Arbitration_Enable flag with an Urgent_Count. The fair/urgent method works as follows:

When the bus is idle for longer than an arbitration reset gap, a fairness interval begins and all nodes set

their Arbitration_Enable flags, while nodes implementing urgent priority set their Urgent_Count to three.

A node that is waiting to send a packet using the fair priority class should begin arbitrating after detecting

a subaction gap as long as its Arbitration _Enable flag is set. When its Arbitration_Enable flag is cleared,

it waits for an arbitration reset gap before it begins arbitrating. When such a node wins an arbitration contest,

it sends a packet without the urgent label and its Arbitration_Enable flag is cleared.

A node that is waiting to send a packet with urgent priority begins arbitrating after detecting a subaction gap

if its Urgent_Count is nonzero. When its Urgent_Count is zero, it waits for an arbitration reset gap before

it begins arbitrating. Whenever such a node wins an arbitration contest, it sends a packet with the urgent

label.

相關PDF資料 |

PDF描述 |

|---|---|

| TSB14AA1T | FPGA (Field-Programmable Gate Array) |

| TSB14C01MHV | IC APEX 20KE FPGA 160K 484-FBGA |

| TSB14C01HV | 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB21LV03MHV | IC APEX 20KE FPGA 200K 484-FBGA |

| TSB21LV03CHV | IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB14AA1PFB | 功能描述:1394 接口集成電路 3.3V 1-port 50/100 Mbps Backplane PHY RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB14AA1PFBG4 | 功能描述:1394 接口集成電路 3.3V 1-port 50/100 Mbps Backplane PHY RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB14AA1T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecomm/Datacomm |

| TSB14AA1TPFB | 功能描述:IC BACKPLANE PHY 3.3V 48-TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標準包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應商設備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| TSB14C01 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

發(fā)布緊急采購,3分鐘左右您將得到回復。