- 您現在的位置:買賣IC網 > PDF目錄382686 > TSB12LV01APZ (Texas Instruments, Inc.) High-Speed Serial-Bus Link-Layer Controller PDF資料下載

參數資料

| 型號: | TSB12LV01APZ |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | High-Speed Serial-Bus Link-Layer Controller |

| 中文描述: | 高速串行總線鏈路層控制器 |

| 文件頁數: | 12/71頁 |

| 文件大小: | 267K |

| 代理商: | TSB12LV01APZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁

1–4

1.4

Terminal Functions

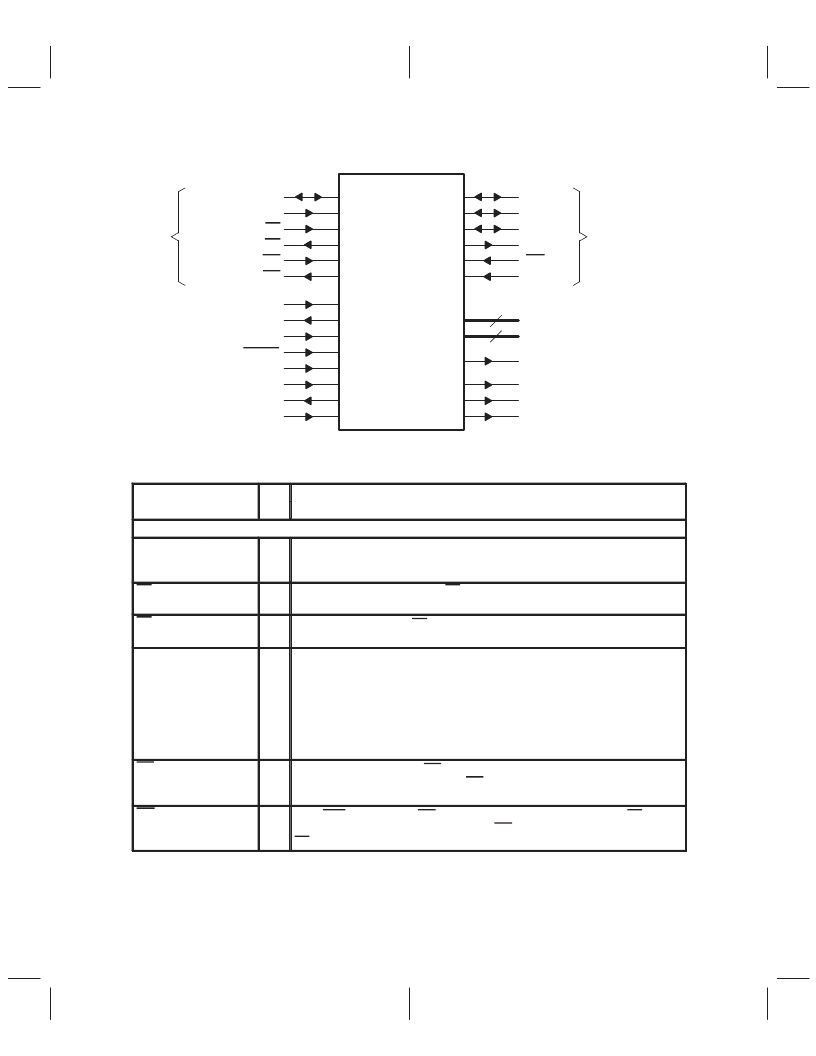

PHY Interface

D0 – D7

CTL0

CTL1

LREQ

ISO

SCLK

DATA0 – DATA31

ADDR0 – ADDR7

CS

CA

WR

INT

CYCLEIN

CYCLEOUT

BCLK

RESET

RAMEZ

NTCLK

NTOUT

NTBIHIZ

VCC

GND

Host

Bus

10

20

TSB12LV01A

CYST

CYDNE

GRFEMP

POWERON

Figure 1–1. TSB12LV01A Terminal Functions

Table 1–1. Terminal Functions

TERMINAL

I/O

DESCRIPTION

NAME

NO.

Host Bus Interface

ADDR0 –

ADDR7

22–25

27–30

I

Address 0 through address 7. Host bus address bus bits 0 through 7 that address

the quadlet-aligned FIFOs and configuration registers. The two least significant

address lines, 6 and 7, must be grounded. Bit 0 is the most significant bit.

CA

35

O

Cycle acknowledge (active low). CA is a TSB12LV01A control signal to the host bus.

When asserted (low), access to the configuration registers or FIFO is complete.

CS

34

I

Cycle start (active low). CS is a host bus control signal to initiate access to the

configuration registers or FIFO.

DATA0 –

DATA31

2–5

7–10

12–15

17–20

82–85

87–90

92–95

97–100

I/O

Data 0 through 31. DATA is a host bus data bus bits 0 through 31. Bit 0 is the most

significant bit. Byte 0 is the most significant byte.

INT

37

O

Interrupt (active low). When INT is asserted (low), the TSB12LV01A notifies the host

bus that an interrupt has occurred. INT is cleared when all the bits INT bits are

cleared in the INT register (or the mask is set false).

WR

36

I

Read/write enable. When WR is deasserted (high) in conjunction with CS, a read

from the TSB12LV01A is requested. When WR is asserted (low) in conjunction with

CS, a write to the TSB12LV01A is requested.

相關PDF資料 |

PDF描述 |

|---|---|

| TSB3055 | IC APEX 20KE FPGA 300K 240-PQFP |

| TSB41AB3 | IC APEX 20KE FPGA 400K 672-FBGA |

| TSB41BA3-EP | IC APEX 20KE FPGA 400K 672-FBGA |

| TSB41LV03PFP | IC APEX 20KE FPGA 600K 652-BGA |

| TSB41AB2I | IEEE 1394a-2000 TWO-PORT CABLE TRANSCEVER/ARBITER |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TSB12LV01B | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394-1995 HIGH SPEED SERIAL BUS LINK LAYER CONTROLLER |

| TSB12LV01B-EP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Military Enhanced Plastic High Performance 1394 3.3V Link Layer for Telecom. Embedded & Indust. App. |

| TSB12LV01BIPZT | 功能描述:1394 接口集成電路 High Perf 1394 3.3V Link Layer RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV01BIPZTEP | 功能描述:1394 接口集成電路 Mil Enh Hi Perf 1394 3.3V Link Layer RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV01BPZ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:BUS CONTROLLER |

發布緊急采購,3分鐘左右您將得到回復。