- 您現在的位置:買賣IC網 > PDF目錄365967 > TSB12LV32-EP IC APEX 20KE FPGA 100K 324-FBGA PDF資料下載

參數資料

| 型號: | TSB12LV32-EP |

| 英文描述: | IC APEX 20KE FPGA 100K 324-FBGA |

| 中文描述: | 軍事增強塑料電機及電子學工程師聯合會1394-1995和P1394a兼容通用鏈路層控制器 |

| 文件頁數: | 100/106頁 |

| 文件大小: | 605K |

| 代理商: | TSB12LV32-EP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁當前第100頁第101頁第102頁第103頁第104頁第105頁第106頁

8

–

7

been transferred. The Phy indicates the end of packet data by asserting idle on the CTL terminals. All

received packets are transferred to the TSB12LV32. Note that the speed code is part of the Phy-LLC

protocol and is not included in the calculation of CRC or any other data protection mechanisms.

It is possible for the Phy to receive a null packet, which consists of the data-prefix state on the serial bus

followed by the data-end state, without any packet data. A null packet is transmitted whenever the packet

speed exceeds the capability of the receiving Phy, or whenever the TSB12LV32 immediately releases the

bus without transmitting any data. In this case, the Phy will assert receive on the CTL terminals with the

data-on indication (all 1s) on the D terminals, followed by idle on the CTL terminals, without any speed code

or data being transferred. In all cases, the TSB41LV03A sends at least one data-on indication before

sending the speed code or terminating the receive operation.

The TSB41LV03A also transfers its own self-ID packet, transmitted during the self-ID phase of bus

initialization, to the TSB12LV32. This packet it transferred to the TSB12LV32 just as any other received

self-ID packet.

00

00

10

00

01

XX

dn

d0

SPD

(a)

(e)

(d)

(b)

(c)

FF (

“

data

–

on

”

)

D0

–

D7

CTL0, CTL1

SYSCLK

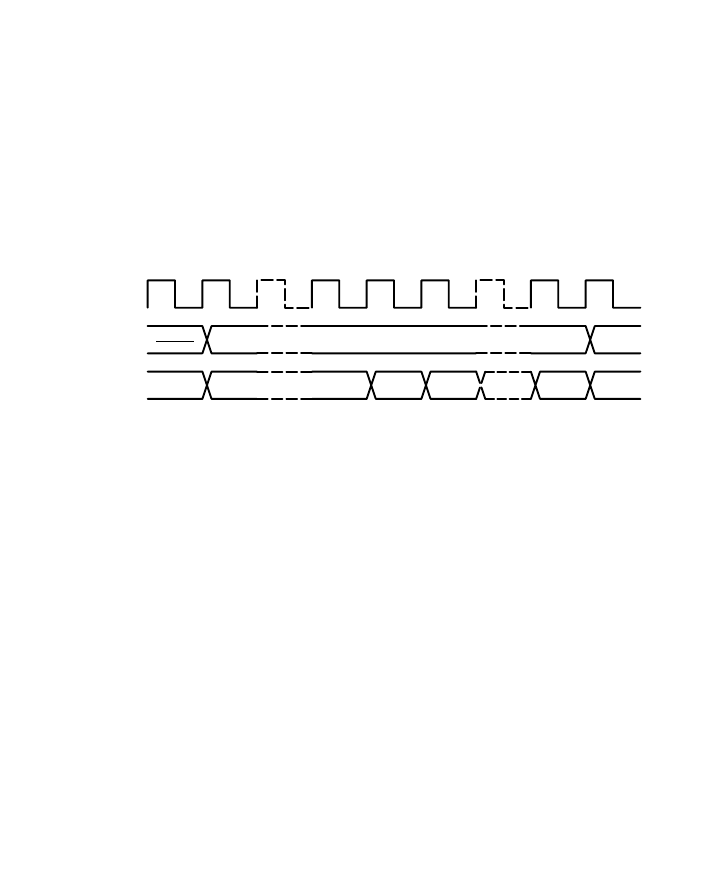

Figure 8

–

4. Normal Packet Reception Timing

The sequence of events for a normal packet reception is as follows:

Receive operation initiated. The Phy indicates a receive operation by asserting receive on the

CTL lines. Normally, the interface is idle when receive is asserted. However, the receive operation

may interrupt a status transfer operation that is in progress so that the CTL lines may change from

status to receive without an intervening idle.

Data-on indication. The Phy asserts the data-on indication code on the D lines for one or more

cycles preceding the speed-code.

Speed-code. The Phy indicates the speed of the received packet by asserting a speed-code on

the D lines for one cycle immediately preceding packet data. The link decodes the speed-code

on the first receive cycle for which the D lines are not the data-on code. If the speed-code is

invalid, or indicates a speed higher than that which the link is capable of handling, the link should

ignore the subsequent data.

Receive data. Following the data-on indication (if any) and the speed-code, the Phy asserts

packet data on the D lines with receive on the CTL lines for the remainder of the receive operation.

Receive operation terminated. The Phy terminates the receive operation by asserting idle on the

CTL lines. The Phy asserts at least one cycle of idle following a receive operation.

相關PDF資料 |

PDF描述 |

|---|---|

| TSB12LV01B-EP | FPGA (Field-Programmable Gate Array) |

| TSB12LV01BPZ | FPGA (Field-Programmable Gate Array) |

| TSB12LV26-EP | 672-pin FineLine BGA |

| TSB12LV22PZP | OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

| TSB12LV26PZ | OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TSB12LV32I | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394-1995 and P1394a Compliant General-Purpose Link-Layer Controller |

| TSB12LV32IPZ | 功能描述:1394 接口集成電路 General-Purpose Link Layer Cntrlr RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV32IPZEP | 制造商:Texas Instruments 功能描述:1394 I-TEMP 1394 GENERAL-PURPOSE LINK LAYER CONTROLLER (GP2L - Rail/Tube |

| TSB12LV32IPZG4 | 功能描述:1394 接口集成電路 General Purpose Link Layer Cntrlr RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV32PZ | 功能描述:1394 接口集成電路 General-Purpose Link Layer Cntrlr RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

發布緊急采購,3分鐘左右您將得到回復。