- 您現在的位置:買賣IC網 > PDF目錄365968 > TSB14AA1T FPGA (Field-Programmable Gate Array) PDF資料下載

參數資料

| 型號: | TSB14AA1T |

| 英文描述: | FPGA (Field-Programmable Gate Array) |

| 中文描述: | 電信提供商/數據通信 |

| 文件頁數: | 22/35頁 |

| 文件大?。?/td> | 224K |

| 代理商: | TSB14AA1T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

6

–

2

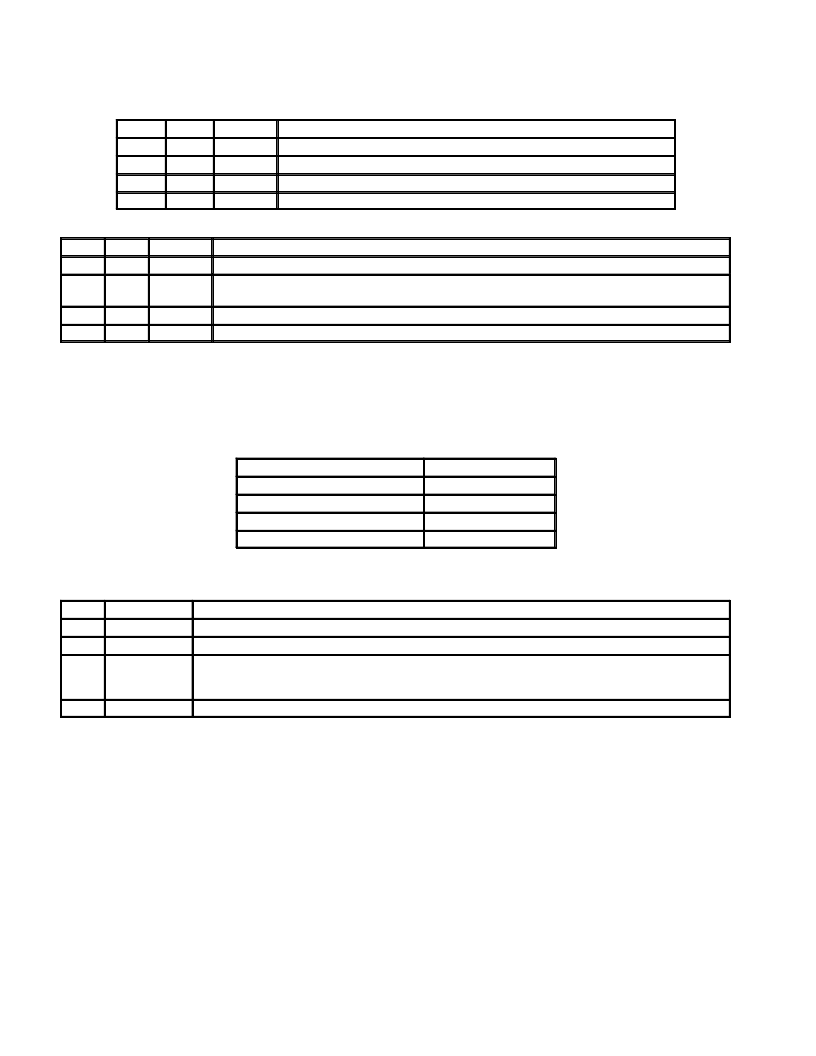

Table 6

–

1. CTL Encoding When PHY Has Control of the Bus

CTL0

CTL1

NAME

DESCRIPTION

0

0

Idle

No activity (this is the default mode)

0

1

Status

Status information is being sent from the PHY to the LLC.

1

0

Receive

An incoming packet is being sent from the PHY to the LLC.

1

1

Grant

The LLC has been given control of the bus to send an outgoing packet.

Table 6

–

2. CTL Encoding When LLC Has Control of the Bus

CTL0

CTL1

NAME

DESCRIPTION

0

0

Idle

The LLC releases the bus (transmission has been completed).

0

1

Hold

The LLC is holding the bus while data is being prepared for transmission, or indicating that another packet is to

be transmitted (concatenated) without arbitrating.

1

0

Transmit

An outgoing packet is being sent from the LLC to the PHY.

1

1

Reserved

Reserved

When the link needs to request the bus or access a register that is located in the TSB14AA1A PHY, a serial stream

of information is sent across the LREQ line. The length of the stream varies depending on whether the transfer is a

bus request, a read command, or a write command (see Table 6

–

3). Regardless of the type of transfer, a start bit of

1 is required at the beginning of the stream, and a stop bit of 0 is required at the end of the stream. Bit 0 is the MSB,

and is transmitted first. The LREQ line is required to idle low (logic level 0).

Table 6

–

3. Request Bit Length

REQUEST TYPE

NUMBER OF BITS

Bus request (cable)

7

Bus request (backplane)

11

Read register request

9

Write register request

17

For a bus request in the cable environment, the length of the LREQ data stream is 7 bits as shown in Table 6

–

4.

Table 6

–

4. Bus Request for Cable Environment

BIT(s)

NAME

DESCRIPTION

0

Start bit

Indicates the beginning of the transfer (always 1)

1

–

3

Request type

Indicates the type of bus request (see Table 6

–

8 for the encoding of this field)

4

–

5

Request speed

Indicates the speed at which the PHY sends the packet for this request. This field has the same encoding as the

speed code from the first symbol of the receive packet. See Table 6

–

5 for the encoding of this field. This field can be

expanded to support data higher than 400 Mbit/s in the future.

6

Stop bit

Indicates the end of the transfer (always 0).

The 14AA1A will accept an LREQ transfer bus request in the backplane format. This request is 11 bits long and has

the format shown in Table 6

–

5. This is an optional feature of the backplane environment; it allows the priority of a

packet to be changed on a packet by packet basis. When using normal cable LREQs that are 7 bits long, the packet

will have the priority contained in the priority register of the TSB14AA1A. For this case to change the priority requires

software to change the value of the priority register inside the PHY.

相關PDF資料 |

PDF描述 |

|---|---|

| TSB14C01MHV | IC APEX 20KE FPGA 160K 484-FBGA |

| TSB14C01HV | 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB21LV03MHV | IC APEX 20KE FPGA 200K 484-FBGA |

| TSB21LV03CHV | IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER |

| TSB2203X6MMX30M | IC APEX 20KE FPGA 200K 240-PQFP |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TSB14AA1TPFB | 功能描述:IC BACKPLANE PHY 3.3V 48-TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標準包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應商設備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| TSB14C01 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB14C01A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB14C01AI | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB14C01AIPM | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

發布緊急采購,3分鐘左右您將得到回復。