- 您現在的位置:買賣IC網 > PDF目錄365968 > TSB14AA1T FPGA (Field-Programmable Gate Array) PDF資料下載

參數資料

| 型號: | TSB14AA1T |

| 英文描述: | FPGA (Field-Programmable Gate Array) |

| 中文描述: | 電信提供商/數據通信 |

| 文件頁數: | 9/35頁 |

| 文件大小: | 224K |

| 代理商: | TSB14AA1T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

1

–

4

1.5

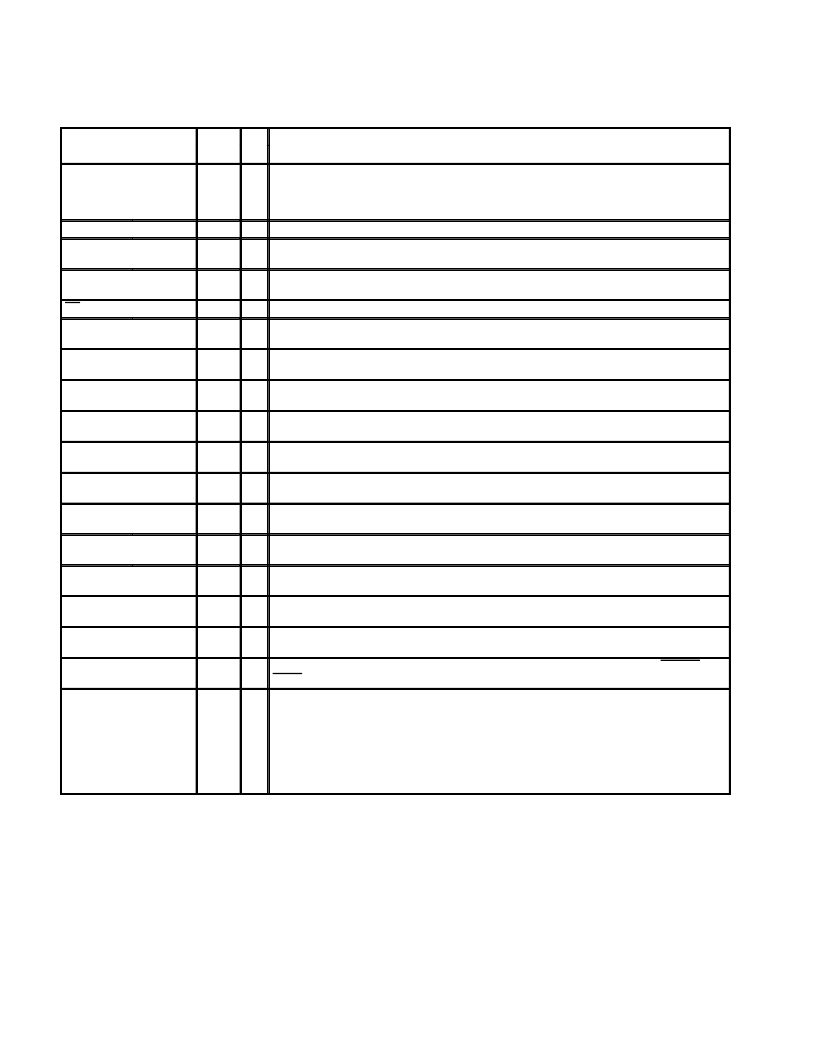

Terminal Descriptions

TERMINAL

TYPE

I/O

DESCRIPTION

NAME

CLK_SEL0

NO.

46

CMOS

I

Clock select 0. If this terminal is set to low (0) then the speed is 98.304 Mbps. If this terminal is set to

high (1) the speed is 49.152 Mbps.

To operate at 100 Mbps requires an input clock of 98.304 MHz. To operate at 49.152 Mbps requires

an input clock of 49.152 MHz.

Clock select 1. CLK_SEL1 must be tied to ground during normal operation.

CLK_SEL1

47

CMOS

I

CTL0, CTL1

7, 8

CMOS

I/O

Control I/O. These are bidirectional signals that communicate between the TSB14AA1A and the

link layer that controls the passage of information between the two devices.

Data I/O. These are bidirectional information signals that communicate the data between the

TSB14AA1A and the link layer controller.

Enable on-chip regulator. This active low pin enables the 1.8 V on

–

chip regulator.

D0, D1

10, 12

CMOS

I/O

EN

38

Supply

I

EX_ID0

19

CMOS

I

External ID 0. The state of this pin sets the value of bit 0 of the

PHYSICAL_ID

field in the

NODE ID

Register upon hardware or SWHRST reset. The register bit may be modified by software.

External ID 1. The state of this pin sets the value of bit 1 of the

PHYSICAL_ID

field in the

NODE ID

register upon hardware or SWHRST reset. The register bit may be modified by software.

External ID 2. The state of this pin sets the value of bit 2 of the

PHYSICAL_ID

field in the

NODE ID

register upon hardware or SWHRST reset. The register bit may be modified by software.

External ID 3. The state of this pin sets the value of bit 3 of the

PHYSICAL_ID

field in the

NODE ID

register upon hardware or SWHRST reset. The register bit may be modified by software.

External ID 4. The state of this pin sets the value of bit 4 of the

PHYSICAL_ID

field in the

NODE ID

register upon hardware or SWHRST reset. The register bit may be modified by software.

External ID 5. The state of this pin sets the value of bit 5 of the

PHYSICAL_ID

field in the

NODE ID

register upon hardware or SWHRST reset. The register bit may be modified by software.

External priority 0. The state of this pin sets the value of bit 0 of the

PRIORITY

field in the

PRIORITY

register upon hardware or SWHRST reset. The register bit may be modified by software.

External priority 1. The state of this pin sets the value of bit 1 of the

PRIORITY

field in the

PRIORITY

register upon hardware or SWHRST reset. The register bit may be modified by software.

External priority 2. The state of this pin sets the value of bit 2 of the

PRIORITY

field in the

PRIORITY

register upon hardware or SWHRST reset. The register bit may be modified by software.

External priority 3. The state of this pin sets the value of bit 3 of the

PRIORITY

field in the

PRIORITY

register upon hardware or SWHRST reset. The register bit may be modified by software.

Ground voltage reference

EX_ID1

20

CMOS

I

EX_ID2

21

CMOS

I

EX_ID3

22

CMOS

I

EX_ID4

23

CMOS

I

EX_ID5

24

CMOS

I

EX_PR0

13

CMOS

I

EX_PR1

14

CMOS

I

EX_PR2

15

CMOS

I

EX_PR3

16

CMOS

I

GND

4, 18, 28,

32, 34, 44

9

Supply

IDS

CMOS

I

Invert data strobe. When this pin is set low, the TDATA, TSTRB, RDATA, RSTRB, OCDOE, and

TDOE pins operate normally (i.e., true). When this pin is set high, these six pins are inverted.

Link-On output. This pin notifies the LLC to power-up and become active. LINKON is a square-wave

signal with a frequency between 4 and 8 MHz when active. LINKON is otherwise driven low, except

during a hardware reset when it is high impedance.

LINKON is activated if the LPS is inactive (LLC inactive) and when the PHY receives a link-on PHY

packet addressed to this node.

Once activated, LINKON will continue active until the LPS becomes active (LLC active). The PHY

also deasserts (low) LINKON when a bus-reset occurs.

LINKON

2

CMOS

O

相關PDF資料 |

PDF描述 |

|---|---|

| TSB14C01MHV | IC APEX 20KE FPGA 160K 484-FBGA |

| TSB14C01HV | 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB21LV03MHV | IC APEX 20KE FPGA 200K 484-FBGA |

| TSB21LV03CHV | IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER |

| TSB2203X6MMX30M | IC APEX 20KE FPGA 200K 240-PQFP |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TSB14AA1TPFB | 功能描述:IC BACKPLANE PHY 3.3V 48-TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標準包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應商設備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| TSB14C01 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB14C01A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB14C01AI | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB14C01AIPM | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

發布緊急采購,3分鐘左右您將得到回復。