- 您現在的位置:買賣IC網 > PDF目錄365968 > TSB14AA1T FPGA (Field-Programmable Gate Array) PDF資料下載

參數資料

| 型號: | TSB14AA1T |

| 英文描述: | FPGA (Field-Programmable Gate Array) |

| 中文描述: | 電信提供商/數據通信 |

| 文件頁數: | 27/35頁 |

| 文件大小: | 224K |

| 代理商: | TSB14AA1T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

6

–

7

6.2

Backplane Environment

6.2.1

Backplane PHY Connection

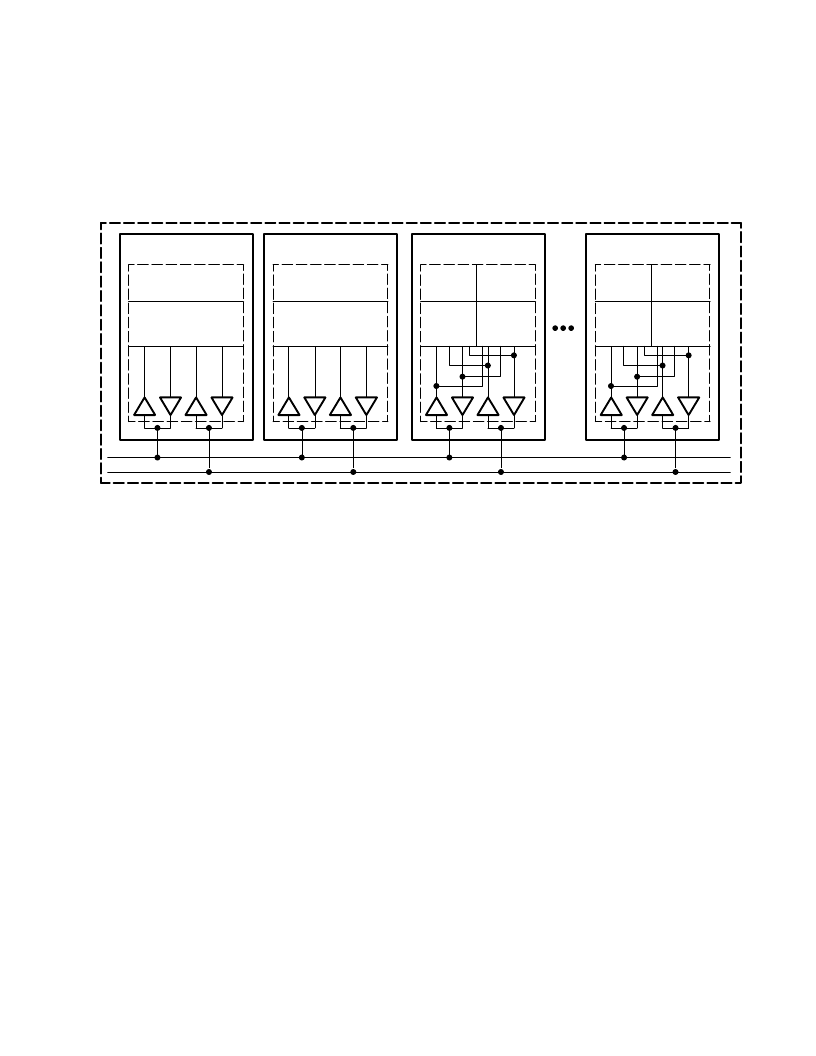

Typically within a single ended signaling backplane environment, the serial bus is implemented with a pair of signals

(STRB and DATA). The topology is a simple pair of bussed signals as shown in Figure 6

–

6.

PHY

Node

Module

PHY

Node

Module

PHY

Node

Module

PHY

Node

PHY

Node

Module

PHY

Node

STRB

DATA

Backplane Chassis

Figure 6

–

6. Backplane Topology

NOTE:

On a given bus, there can be as many as 63 nodes. There is no restriction on the

distribution of nodes throughout modules on the bus. When more than one node occupies a

module, they must share the same transceivers.

The backplane environment can be implemented with a number of different interface technologies. These include,

but are not limited to: industry-standard gunning transistor logic plus (GTLP), industry-standard transistor-transistor

logic (TTL), backplane transceiver logic (BTL) as defined by IEEE Std 1194 [10] and emitter-coupled logic (ECL).

In addition to the requirements specified by the application environment, the physical media or the serial bus should

meet the requirements defined for media attachment, media signal interface, and media signal timing. Timing

requirements must be met over the ranges specified in the application environment. These include temperature

ranges, voltage ranges, and manufacturing tolerances.

6.2.2

Definition of Logic States

In the open collector environment, the drivers assert the bus to indicate a 1 logic state, or release the bus to indicate

a 0 logic state. To assert the bus, an open collector driver sinks current. To release the bus, drivers are asserted to

a high-impedance state or turned off, allowing the bus signal to be pulled to the termination voltage of the bus.

NOTE:

This typically results in a logical inversion of signals on GTLP, TTL and BTL buses.

Signals on ECL buses typically are not inverted.

All drivers operate in a wired-ORed mode during arbitration. Drivers can operate in a totem pole mode during data

packet and acknowledge transfers. In this mode, a driver can drive the bus into its released state to decrease the rise

time of the bus signal (referred to as a rescinding release with TTL technology).

6.2.3

Bit Rates

Data transmission and reception occurs at 49.152 Mbit/s or 98.304 Mbit/s (

±

100 ppm). In normal operation,

regardless of the interface technology, arbitration occurs at an arbitration clock rate of 49.152 MHz.

[10]

IEEE Std 1194.1

–

1991, IEEE Standard for Electrical Characteristics of Backplane Transceiver Logic (BTL) Interface Circuits

相關PDF資料 |

PDF描述 |

|---|---|

| TSB14C01MHV | IC APEX 20KE FPGA 160K 484-FBGA |

| TSB14C01HV | 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB21LV03MHV | IC APEX 20KE FPGA 200K 484-FBGA |

| TSB21LV03CHV | IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER |

| TSB2203X6MMX30M | IC APEX 20KE FPGA 200K 240-PQFP |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TSB14AA1TPFB | 功能描述:IC BACKPLANE PHY 3.3V 48-TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標準包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應商設備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| TSB14C01 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB14C01A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB14C01AI | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB14C01AIPM | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

發布緊急采購,3分鐘左右您將得到回復。