- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365968 > TSB14AA1T FPGA (Field-Programmable Gate Array) PDF資料下載

參數(shù)資料

| 型號: | TSB14AA1T |

| 英文描述: | FPGA (Field-Programmable Gate Array) |

| 中文描述: | 電信提供商/數(shù)據(jù)通信 |

| 文件頁數(shù): | 25/35頁 |

| 文件大小: | 224K |

| 代理商: | TSB14AA1T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

6

–

5

Table 6

–

9. Status Bit Description

BIT(s)

NAME

DESCRIPTION

0

Arbitration

Reset Gap

Indicates that the PHY has detected that the bus has been idle for an arbitration reset gap time. This time is defined

in the 1394

–

1995 standard

. This bit is used by the link in its busy/retry state machine.

1

Subaction Gap

Indicates that the PHY has detected that the bus has been idle for a subaction gap time. This time is defined in the

1394 standard.

2

Bus Reset

Indicates that the PHY has entered the bus reset state

3

Reserved

Reserved

4

–

7

Address

Holds the address of the PHY register whose contents are transferred to the link

8

–

15

IEEE Std 1394

–

1995,

IEEE Standard for a High Performance Serial Bus

Data

Indicates the data that is to be sent to the link

PHY

Ctl[0:1]

PHY

D[0:1]

00

00

01

01

00

00

S[0,1]

S[2,3]

01

00

00

S[14,15]

00

00

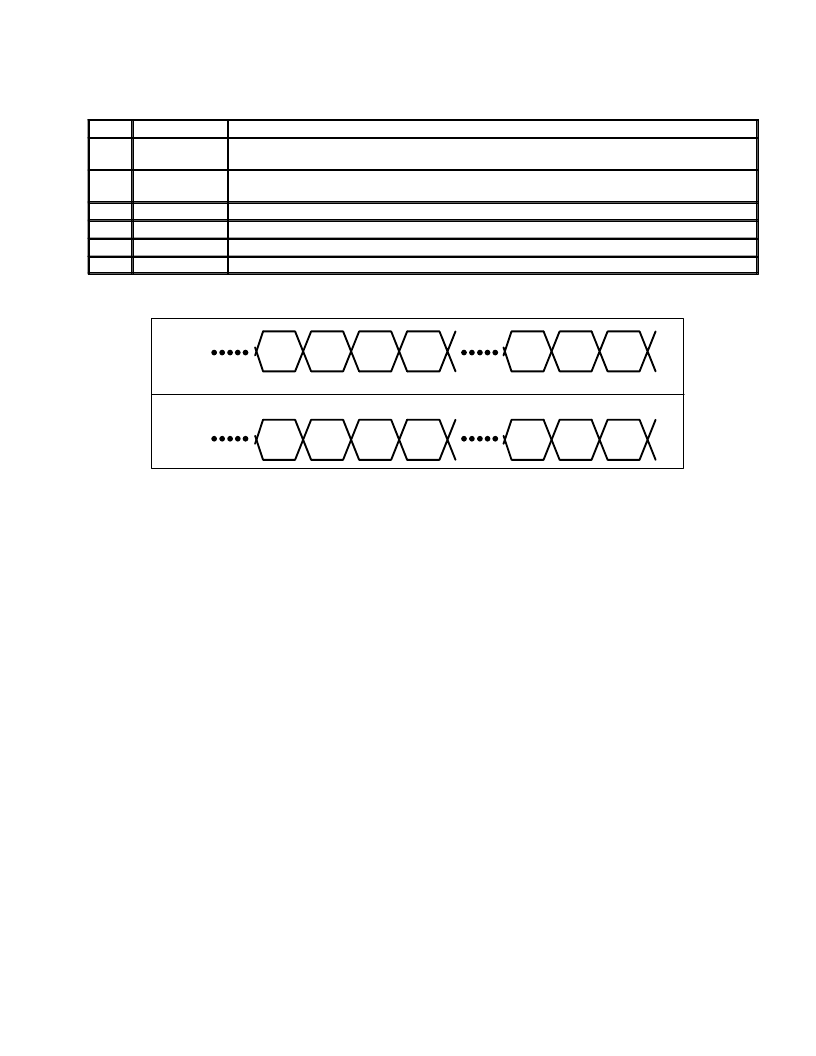

Figure 6

–

3. Status Transfer Timing

6.1.4

Transmit

When the link requests access to the serial bus through the LREQ terminal, the PHY arbitrates for access to the serial

bus. When the PHY wins the arbitration, it grants the bus to the link by asserting transmit on the CTL terminals for

one SCLK cycle, followed by idle for one cycle. After sampling the transmit state from the PHY, the link takes over

control of the interface by asserting either hold or transmit on the CTL terminals. The link asserts hold to keep

ownership of the bus while preparing data. The PHY asserts the data-on state on the serial bus during this time. When

it is ready to begin transmitting a packet, the link asserts transmit on the CTL terminals along with the first bits of the

packet. After sending the last bits of the packet, the link asserts either idle or hold on the CTL terminals for one cycle,

and then idle for one additional cycle before asserting those terminals to a high-impedance state.

The hold state indicates to the PHY that the link needs to send another packet without releasing the bus. The PHY

responds to this hold state by waiting the required minimum time and then asserting transmit as before. This function

is used after sending an acknowledgement if the link intends to send a unified response, during a single cycle. The

only requirement when sending multiples packet during bus ownership is that all packets must be transmitted at the

same speed, since the speed of the packet transmission is set before the first packet.

As noted above, when the link has finished sending the last packet for the current bus ownership, it releases the bus

by asserting idle on the CTL terminals for two SCLK cycles. The PHY begins asserting idle on the CTL terminals one

clock cycle after sampling the second idle from the link. Whenever the D and CTL links change ownership between

the PHY and the link, there is an extra clock period allowed so that both sides of the interface can operate on registered

versions of the interface signals, rather than having to respond to a CTL state on the next cycle.

It is not required that the link enter the hold state before sending the first packet when implementation permits the

link to be ready to transmit as soon as bus ownership is granted. The timing of a single packet transmit operation is

shown in Figure 6

–

4. In the diagram, D0

–

Dn are the data symbols of the packet, ZZ represents the high-impedance

state.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSB14C01MHV | IC APEX 20KE FPGA 160K 484-FBGA |

| TSB14C01HV | 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB21LV03MHV | IC APEX 20KE FPGA 200K 484-FBGA |

| TSB21LV03CHV | IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER |

| TSB2203X6MMX30M | IC APEX 20KE FPGA 200K 240-PQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB14AA1TPFB | 功能描述:IC BACKPLANE PHY 3.3V 48-TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| TSB14C01 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB14C01A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB14C01AI | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB14C01AIPM | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。