- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365968 > TSB14AA1T FPGA (Field-Programmable Gate Array) PDF資料下載

參數(shù)資料

| 型號: | TSB14AA1T |

| 英文描述: | FPGA (Field-Programmable Gate Array) |

| 中文描述: | 電信提供商/數(shù)據(jù)通信 |

| 文件頁數(shù): | 28/35頁 |

| 文件大小: | 224K |

| 代理商: | TSB14AA1T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當(dāng)前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

6

–

8

6.2.4

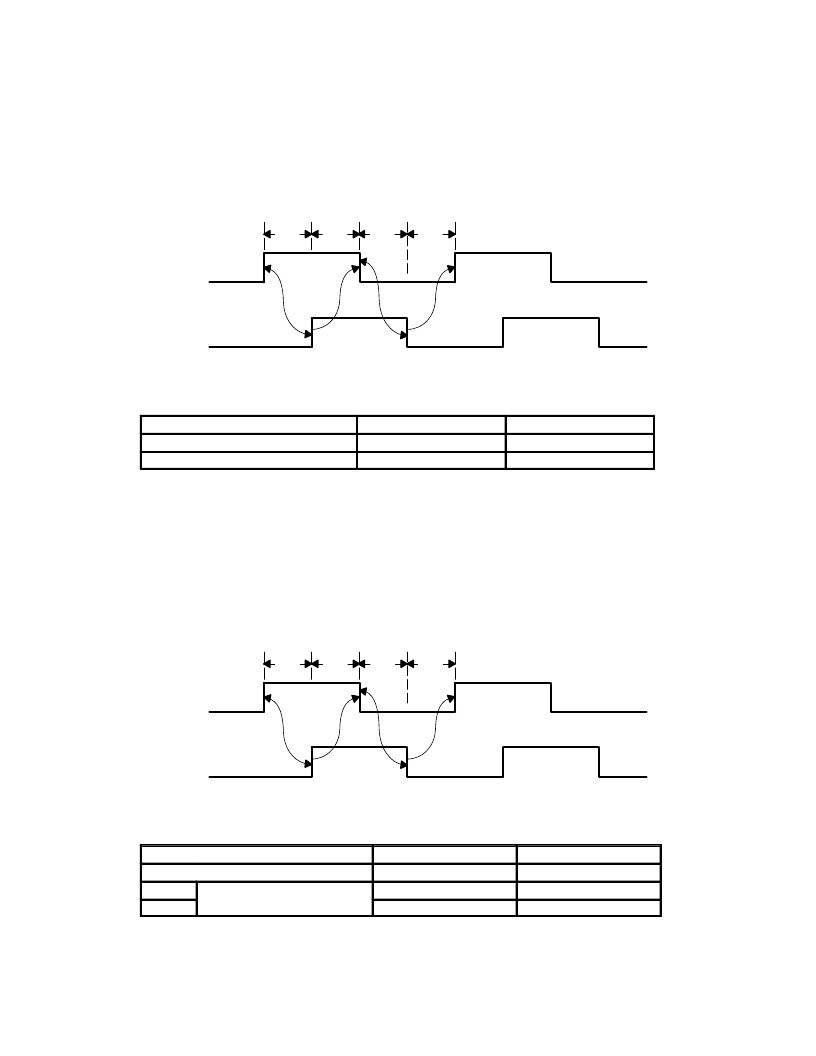

Backplane Transmit Data Timing

Edge separation is the minimum required time between any two consecutive transitions of the backplane bus signals,

as they appear from the output of the transmitters, whether they are transitions on the same signal or transitions on

the two separate signals. A minimum edge separation is required to ensure proper operation of the data strobe

bit-level encoding mechanism. TDATA and TSTRB have the relationship shown in Figure 6

–

7 and Table 6

–

10.

t(2)

t(2)

t(1)

TDATA

TSTRB

t(2)

t(2)

t(1)

t(1)

t(1)

Figure 6

–

7. Minimum Edge Separation

Table 6

–

10. TSB14AA1A to Backplane Transceiver Timing

PARAMETER

98.304 MHz

49.152 MHz

t(1)

t(2)

This parameter is based on a maximum total transmit skew of 2 ns.

Bit cell period for data

9.44 ns minimum

19.44 ns minimum

Transmit (Tx) edge separation

8.65 ns minimum

18.65 ns minimum

6.2.5

Backplane Receive Data Timing

The receiver typically uses the transitions on the incoming bus signals RDATA and RSTRB to derive a clock at the

code bit frequency to extract the NRZ signal on RDATA. This clock can be derived by performing an exclusive-OR

(XOR) of RDATA and RSTRB.

The bus signals, as they appear from the backplane transceiver media and into the receiver, should fall within the

timing constraints outlined by Figure 6

–

8.

RDATA

RSTRB

t(3)

t(1)

t(1)

t(1)

t(1)

t(2)

t(3)

t(2)

Figure 6

–

8. Backplane Receive Data Timing

Table 6

–

11. TSB14AA1A to Backplane Transceiver Timing

PARAMETER

98.304 MHz

49.152 MHz

t(1)

t(2)

t(3)

This parameter is based on a maximum total transmit skew of 2 ns and a maximum backplane skew of 0.5 ns.

This assumes total receive skew is less than receive edge separation (i.e., some skew margin exists).

Bit cell period

10.1715 ns nominal

20.34 nominal

Receive (Rx) edge separation

3.4 ns minimum

16.3 ns maximum

3.4 ns minimum

36.6 ns maximum

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSB14C01MHV | IC APEX 20KE FPGA 160K 484-FBGA |

| TSB14C01HV | 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB21LV03MHV | IC APEX 20KE FPGA 200K 484-FBGA |

| TSB21LV03CHV | IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER |

| TSB2203X6MMX30M | IC APEX 20KE FPGA 200K 240-PQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB14AA1TPFB | 功能描述:IC BACKPLANE PHY 3.3V 48-TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| TSB14C01 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB14C01A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB14C01AI | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB14C01AIPM | 制造商:TI 制造商全稱:Texas Instruments 功能描述:5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。