- 您現在的位置:買賣IC網 > PDF目錄373969 > AD9862 (Analog Devices, Inc.) Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications PDF資料下載

參數資料

| 型號: | AD9862 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

| 中文描述: | 混合寬帶通信信號前端(MxFE⑩)處理器 |

| 文件頁數: | 10/32頁 |

| 文件大小: | 617K |

| 代理商: | AD9862 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

REV. 0

–10–

AD9860/AD9862

FFT OUTPUT – MHz

5

F

20

–20

–40

–60

–80

10

15

25

30

0

–100

–120

0

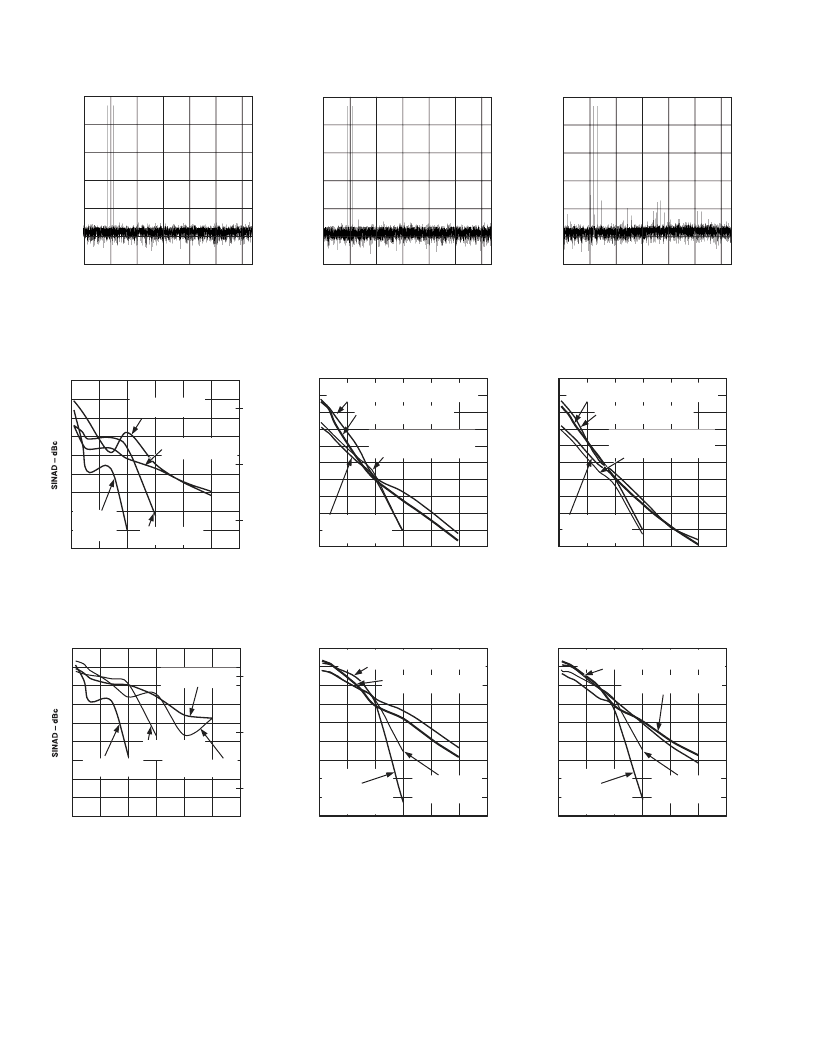

TPC 10. ADC Dual Tone FFT with

Buffer Tones at 4.5 MHz and 5.5 MHz

f

IN

– MHz

0

200

50

60

58

56

54

50

62

11.0

8.0

8.5

10.0

10.5

9.5

9.0

150

250

100

64

66

68

BUFFERED 1V

INPUT, 2 GAIN

BUFFERED

2V INPUT,

1

GAIN

BUFFERED BYPASS

1V INPUT, 2 GAIN

BUFFERED BYPASS

2V INPUT, 1 GAIN

52

300

TPC 13. AD9862 Rx SINAD

vs. f

IN

at 64 MSPS

f

IN

– MHz

0

200

50

60

58

56

54

52

50

48

62

46

44

10.0

7.0

7.5

9.0

9.5

8.5

8.0

150

250

100

BUFFERED BYPASS

1V INPUT, 2 GAIN

BUFFERED 1V

INPUT, 2 GAIN

BUFFERED BYPASS

2V INPUT, 1 GAIN

BUFFERED 2V

INPUT, 1 GAIN

300

TPC 16. AD9860 Rx SINAD

vs. f

IN

at 64 MSPS

FFT OUTPUT – MHz

5

F

20

–20

–40

–60

–80

10

15

25

30

0

–100

–120

0

TPC 11. ADC Dual Tone FFT without

Buffer Tones at 4.5 MHz and 5.5 MHz

f

IN

– MHz

0

200

50

S

60

58

56

54

52

50

62

150

250

100

64

66

68

70

300

LOW POWER MODE 1, BUFFER BYPASSED,

2V p-p INPUT, 1

RxPGA GAIN

BUFFER BYPASSED, 2V p-p,

1

RxPGA GAIN

LOW POWER MODE 1, BUFFER

ENABLED, 1V p-p INPUT,

2

RxPGA GAIN

BUFFER ENABLED,

1V p-p INPUT,

2

RxPGA GAIN

TPC 14. AD9862 Rx SINAD

vs. f

IN

at 32 MSPS

f

IN

– MHz

0

200

50

S

52

50

48

46

44

54

150

250

100

56

58

60

62

300

LOW POWER MODE 1, BUFFER BYPASSED,

2V p-p INPUT, 1

RxPGA GAIN

BUFFER BYPASSED, 2V p-p,

1

RxPGA GAIN

LOW POWER

MODE 1,

BUFFER ENABLED,

1V p-p INPUT,

2

RxPGA GAIN

BUFFER ENABLED,

1V p-p INPUT,

2

RxPGA GAIN

TPC 17. AD9860 Rx SINAD

vs. f

IN

at 32 MSPS

FFT OUTPUT – MHz

5

F

20

–20

–40

–60

–80

10

15

25

30

0

–100

–120

0

TPC 12. ADC Dual Tone FFT

(undersampling) without Buffer

Tones at 69.5 MHz and 70.5 MHz

f

IN

– MHz

0

200

50

S

60

58

56

54

52

50

62

150

250

100

64

66

68

70

300

LOW POWER MODE 2, BUFFER BYPASSED,

2V p-p INPUT, 1

RxPGA GAIN

BUFFER BYPASSED, 2V p-p,

1

RxPGA GAIN

LOW POWER MODE 2, BUFFER

ENABLED, 1V p-p INPUT,

2

RxPGA GAIN

BUFFER ENABLED,

1V p-p INPUT,

2

RxPGA GAIN

TPC 15. AD9862 Rx SINAD

vs. f

IN

at 16 MSPS

f

IN

– MHz

0

200

50

S

52

50

48

46

44

54

150

250

100

56

58

60

62

300

LOW POWER MODE 2, BUFFER BYPASSED,

2V p-p INPUT, 1

RxPGA GAIN

BUFFER BYPASSED, 2V p-p,

1

RxPGA GAIN

LOW POWER

MODE 2,

BUFFER ENABLED,

1V p-p INPUT,

2

RxPGA GAIN

BUFFER ENABLED,

1V p-p INPUT,

2

RxPGA GAIN

TPC 18. AD9860 Rx SINAD

vs. f

IN

at 16 MSPS

相關PDF資料 |

PDF描述 |

|---|---|

| AD9862BST | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

| AD9864 | IF Digitizing Subsystem |

| AD9864-EB | IF Digitizing Subsystem |

| AD9864BCPZ | IF Digitizing Subsystem |

| AD9864BCPZRL | IF Digitizing Subsystem |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9862BST | 制造商:Analog Devices 功能描述:Mixed Signal Front End 128-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:12B MIXED SIGNAL FRONT END MXFE PROCESSO - Tape and Reel |

| AD9862BSTRL | 制造商:Analog Devices 功能描述:Mixed Signal Front End 128-Pin LQFP T/R 制造商:Rochester Electronics LLC 功能描述:12B MIXED SIGNAL FRONT END MXFE PROCESSO - Tape and Reel |

| AD9862BSTZ | 功能描述:IC FRONT-END MIXED-SGNL 128-LQFP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點:- 封裝/外殼:48-TQFP 裸露焊盤 供應商設備封裝:48-TQFP 裸露焊盤(7x7) 包裝:托盤 |

| AD9862BSTZRL | 功能描述:IC PROCESSOR FRONT END 128LQFP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點:- 封裝/外殼:48-TQFP 裸露焊盤 供應商設備封裝:48-TQFP 裸露焊盤(7x7) 包裝:托盤 |

| AD9862-EB | 制造商:Analog Devices 功能描述: 制造商:Analog Devices 功能描述:MIXED SIGNAL FRONT END - Bulk |

發布緊急采購,3分鐘左右您將得到回復。