- 您現在的位置:買賣IC網 > PDF目錄373969 > AD9862 (Analog Devices, Inc.) Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications PDF資料下載

參數資料

| 型號: | AD9862 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

| 中文描述: | 混合寬帶通信信號前端(MxFE⑩)處理器 |

| 文件頁數: | 19/32頁 |

| 文件大小: | 617K |

| 代理商: | AD9862 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

REV. 0

AD9860/AD9862

–19–

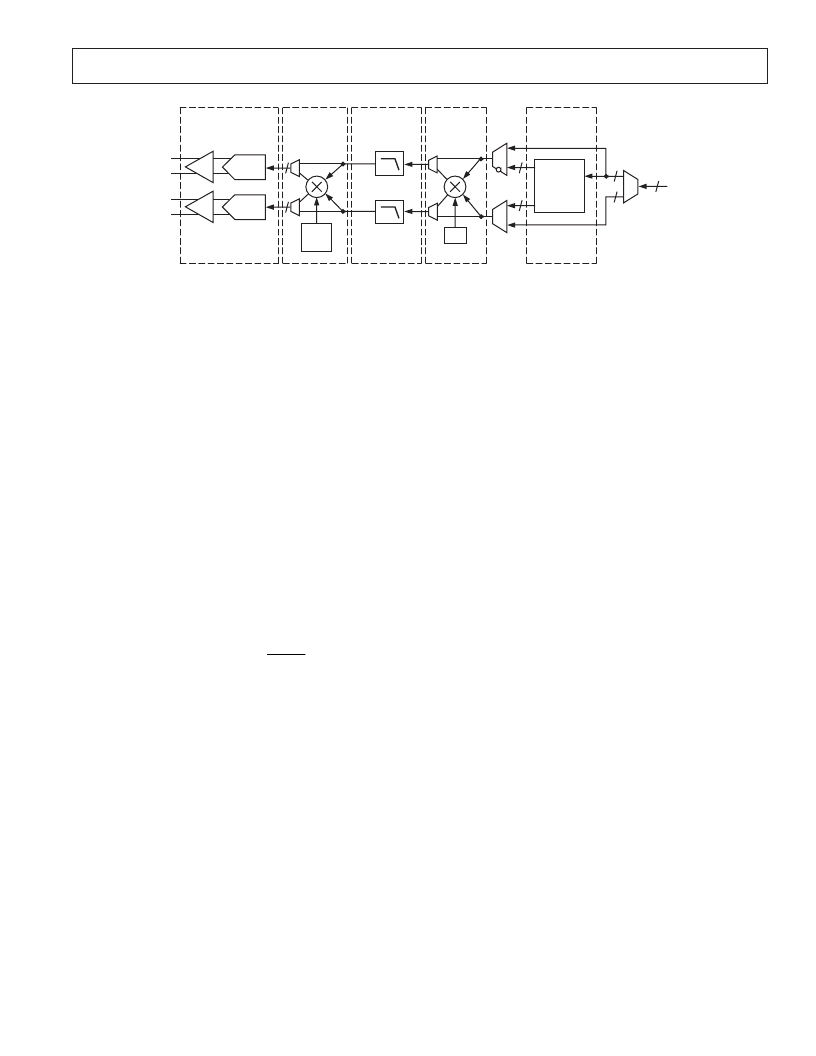

Interpolation Stage (Block C), Fine Modulation Stage (Block D),

Hilbert filter (Block E), and the Latch/Demultiplexing circuitry.

DAC

The DAC stage of the AD9860/AD9862 integrates a high perfor-

mance TxDAC core, a programmable gain control through a

Programmable Gain Amplifier (TxPGA), coarse gain control, and

offset adjustment and fine gain control to compensate for system

mismatches.

The TxDAC core of the AD9860/AD9862 provides dual, differen-

tial, complementary current outputs generated from the 12-/14-bit

data. The 12-/14-bit Dual DACs support update rates up to

128 MSPS. The differential outputs (i.e., IOUT+ and IOUT

–

)

of each dual DAC are complementary, meaning they always sum

to the full-scale current output of the DAC, I

OUTFS

. Optimum

ac performance is achieved with the differential current interface

drives balanced loads or a transformer.

The maximum full-scale output current,

I

OUTFSMAX

, is set by the

external resistor (R

SET

), which sets the DAC reference current.

The R

SET

resistor is connected between the FSADJ Pin to ground.

The relationship between

I

OUTFSMAX

and

R

SET

is:

I

OUTFSMAX

SET

V

R

~

.

67

1 23

¥ê

ˉ

Typically, R

SET

is 4 k

W

, which sets I

OUTFSMAX

to 20 mA, the

optimal dynamic setting for the TxDACs. Increasing R

SET

by a

factor of 2 will proportionally decrease I

OUTFSMAX

by a factor of

2. I

OUTFSMAX

of each DAC can be re-scaled either simulta-

neously with the TxPGA Gain register or independently with

DAC A/B Coarse Gain registers.

The TxPGA function provides 20 dB of simultaneous gain

range for both DACs and is controlled by writing to SPI register

TxPGA Gain for a programmable full-scale output of 10% to

100% I

OUTFSMAX

. The gain curve is linear in dB, with steps of

about 0.1 dB. Internally, the gain is controlled by changing the

main DAC bias currents with an internal TxPGA DAC whose

output is heavily filtered via an on-chip R-C filter to provide

continuous gain transitions. Note, the settling time and band-

width of the TxPGA DAC can be improved by a factor of 2 by

writing to the TxPGA Fast register.

Each DAC has independent coarse gain control. Coarse gain

control can be used to accommodate different I

OUTFS

from the

dual DACs. The coarse full-scale output control can be adjusted

using the DAC A/B Coarse Gain registers to 1/2 or 1/11th of

the nominal full scale current.

Fine Gain controls and dc offset controls can be used to compen-

sate for mismatches (for system level calibration), allowing improved

matching characteristics of the two Tx channels and aiding in suppres-

sing LO feedthrough. This is especially useful in image rejection

architectures. The 10-bit dc offset control of each DAC can be used

independently to provide a

±

12% I

OUTFSMAX

of offset to either

differential pin, thus allowing calibration of any system offsets. The

fine gain control with 5-bit resolution allows the I

OUTFSMAX

of each

DAC to be varied over a

±

4% range, thus allowing compensation

of any DAC or system gain mismatches. Fine gain control is set

through the DAC A/B Fine Gain registers and the offset control

of each DAC is accomplished using DAC A/B Offset registers.

A power-down option allows the user to power down the analog

supply current to both DACs or either DAC, individually. A digital

power-down is also possible through either the Tx PwrDwn

register or the Mode/TxBlank pin.

Coarse Modulator

A digital coarse modulator is available in the transmit path to

shift the spectrum of the input data by

±

f

DAC

/4 or

±

f

DAC

/8. If the

input data consists of complex data, the modulator can be con-

figured to perform a complex modulation of the input spectrum.

If the data in the transmit path is not complex, a real mix can be

performed separately on each channel thereby frequency shifting

the real data and images by f

DAC

/4 or f

DAC

/8. Real or complex

mixing is configured by setting the Real Mix register.

By default, the coarse modulator is bypassed. It can be configured

using Coarse Modulation and Neg Coarse Tune registers.

Interpolation Stage

Interpolation filters are available for use in the AD9860/AD9862

transmit path, providing 1 (bypassed), 2 , or 4 interpolation.

The interpolation filters effectively increase the Tx data rate while

suppressing the original images. The interpolation filters digitally

shift the worst case image further away from the desired signal,

thus reducing the requirements on the analog output reconstruc-

tion filter.

There are two 2 interpolation filters available in the Tx path.

An interpolation rate of 4 is achieved using both interpolation

filters; an interpolation rate of 2 is achieved by enabling only

the first 2 interpolation filter.

The first interpolation filter provides 2 interpolation using a

39 tap filter. It suppresses out-of-band signals by 60 dB or more

and has a flat passband response (less than 0.1 dB ripple) extend-

ing to 38% of the AD9860/AD9862 input Tx data rate (19% of

the DAC update rate, f

DAC

). The maximum input data rate is

64 MSPS per channel when using 2 interpolation.

TxDAC

BYPASSABLE

DIGITAL

QUADRATURE

MIXER

PGA

IOUT+A

IOUT–A

TxDAC

PGA

IOUT+B

IOUT–B

HILBERT

FILTER

BLOCK A

BLOCK B

BLOCK C

BLOCK D

BLOCK E

HILBERT

FILTER

DDS

BYPASSABLE

LOW-PASS

INTERPOLATION

FILTER

BYPASSABLE

DIGITAL

QUADRATURE

MIXER

f

S

/4,

f

S

/8

DAC

I

Q

TxDATA

[0:13]

Figure 3. Transmit Section Block Diagram

相關PDF資料 |

PDF描述 |

|---|---|

| AD9862BST | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

| AD9864 | IF Digitizing Subsystem |

| AD9864-EB | IF Digitizing Subsystem |

| AD9864BCPZ | IF Digitizing Subsystem |

| AD9864BCPZRL | IF Digitizing Subsystem |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9862BST | 制造商:Analog Devices 功能描述:Mixed Signal Front End 128-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:12B MIXED SIGNAL FRONT END MXFE PROCESSO - Tape and Reel |

| AD9862BSTRL | 制造商:Analog Devices 功能描述:Mixed Signal Front End 128-Pin LQFP T/R 制造商:Rochester Electronics LLC 功能描述:12B MIXED SIGNAL FRONT END MXFE PROCESSO - Tape and Reel |

| AD9862BSTZ | 功能描述:IC FRONT-END MIXED-SGNL 128-LQFP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點:- 封裝/外殼:48-TQFP 裸露焊盤 供應商設備封裝:48-TQFP 裸露焊盤(7x7) 包裝:托盤 |

| AD9862BSTZRL | 功能描述:IC PROCESSOR FRONT END 128LQFP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點:- 封裝/外殼:48-TQFP 裸露焊盤 供應商設備封裝:48-TQFP 裸露焊盤(7x7) 包裝:托盤 |

| AD9862-EB | 制造商:Analog Devices 功能描述: 制造商:Analog Devices 功能描述:MIXED SIGNAL FRONT END - Bulk |

發布緊急采購,3分鐘左右您將得到回復。