- 您現在的位置:買賣IC網 > PDF目錄373969 > AD9862 (Analog Devices, Inc.) Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications PDF資料下載

參數資料

| 型號: | AD9862 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

| 中文描述: | 混合寬帶通信信號前端(MxFE⑩)處理器 |

| 文件頁數: | 28/32頁 |

| 文件大小: | 617K |

| 代理商: | AD9862 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁

REV. 0

–28–

AD9860/AD9862

The timing block diagrams in Figures 10 and 11 show how the

various clocks of the single and dual Tx path are affected by the

various register settings.

For dual Tx data, an option to redirect demultiplexed data to

either path is available. For example, the AD9860/AD9862 can

accept complex data in the form of I then Q data or Q then I data,

controlled through QI Order register.

For the dual Tx data cases, the Tx_SYNC Pin input logic level

defines what data is currently on the Tx data bus. By default, when

Tx_SYNC is low, Channel A data (first of the set) should be on

the data bus; if TxSYNC is high, Channel B data (or the second of

the set) should be on the Tx bus. This can be reversed be setting

the Inv TxSYNC register.

Rx Path (Alternative Timing Operation)

The ADC sampling rate, the Rx data output rate and the rate of

CLKOUT1 (clock used to latch output data) are the parameters of

interest for the receive path data. These parameters, in addition

to the data bandwidth, are related to CLKIN by decimation filters,

divide by two circuits, data multiplexer logic retiming latches and

also the DLL multiplication setting (which is not the case for

Normal Operation mode). This mode can be configured by

default by forcing the Tx_Blank_In pin to a logic high level during

power up.

The Rx path timing can be broken into two separate relationships:

the ADC sample rate relative to the input clock, CLKIN and

the output data rate relative to CLKOUT1.

The ADCs sample rate relative to CLKIN is controlled by the ADC

Div2 register and the DLL Multiplier register. The sample rate

can be equal to or one half of the DLL output clock rate.

The output data rate relative to CLKOUT1 for the Alternative

Operation Mode has the same configuration options as in the

Normal Operation Mode. The different options are shown in

Figure 9. Table Ia. and Ib. describe the setup required to obtain

the desired data timing.

The Rx data (unless retimed using the Rx Retime register) is

timed relative to the CLKOUT1 pin output. The Rx output data

can be decimated (halving the data rate) or both channels can be

multiplexed onto the Channel A data bus (doubling the data rate).

Decimation enables oversampling while maintaining a slower

external data transfer rate and provides superior suppression of

out of band signals and noise. Multiplexing enables fewer digital

output bits to be used to transfer data from the Rx path to the

digital ASIC collecting the data.

When Multiplexing mode is enabled with an output data rate equal

to CLKOUT1 (Timing No. 3 in Figure 9), then the RxSync pin

is required to identify which channel

’

s output data is on the

output data bus. RxSync output is aligned with the output data

and by default, a logic low indicates data from Rx Channel B is

currently on the output data bus. If RxSync is logic high, then data

from Rx Channel A is currently on the output data bus. The Inv

RxSync register can be used to switch this notation.

The CLKOUT1 pin outputs a clock at a frequency of CLKIN or

CLKIN/2 depending on the voltage level applied to the CLKSEL

pin. If a logic low is applied to CLKSEL, CLKOUT1 will run at

half the CLKIN rate; if CLKSEL is set to logic high, CLKOUT1

outputs a clock equal to CLKIN.

This timing flexibility, along with the invert option for CLKOUT1

controlled by the Inv 1 Register, allows for various methods of

latching data from the Rx path to the digital ASIC, which will pro-

cess the data. These options are shown in Table Ia and Ib along

with a timing diagram in Figure 9. Not shown is the option to

invert CLKOUT1, controlled by the Inv 1 register. For this

mode, relative timing remains the same except the opposite edges

of CLKOUT1 would be used.

Overall, relative timing can be found by using the Alternative

Operation Mode Master Timing Guide in Table V and using Rx

timing shown in Figure 9.

Tx Path (Alternative Timing Operation)

The DAC update rate, the Tx input data rate and the rate of

CLKOUT2 (clock used to latch Tx input data) are the parameters

of interest for the transmit path data. These parameters in addi-

tion to the output signal bandwidth are related to CLKIN by the

settings of the DLL multiplier, the CLKOUT2 Div, the two edge

and the Interpolation registers (in this mode, the ADC Div2

register does not affect Tx timing).

The Tx data is timed relative to the CLKOUT2 pin (unless it is

retimed relative to CLKOUT1 by setting Tx Retime register) and

remains the same as it does in Normal Operation Mode. The input

Tx data is latched on each rising edge, each falling edge or both

edges (controlled through the Inverse Sample and two edge regis-

ters). The timing diagrams for these cases are shown in Figure 12.

The Dual Tx data is multiplexed onto a single bus so that fewer

digital bits are necessary to transfer data. Throughout this discus-

sion of Tx path timing, Tx digital processing options other than

interpolation are ignored because they do not change data timing;

Tx data timing reflects whether single or dual channel data is

latched into the AD9860/AD9862.

The rates of CLKOUT2 (and the input data rate) are related to

CLKIN by the DLL Multiplier register and the setting of the

CLKOUT2 Divide Factor register. These relationships are shown

in Table III.

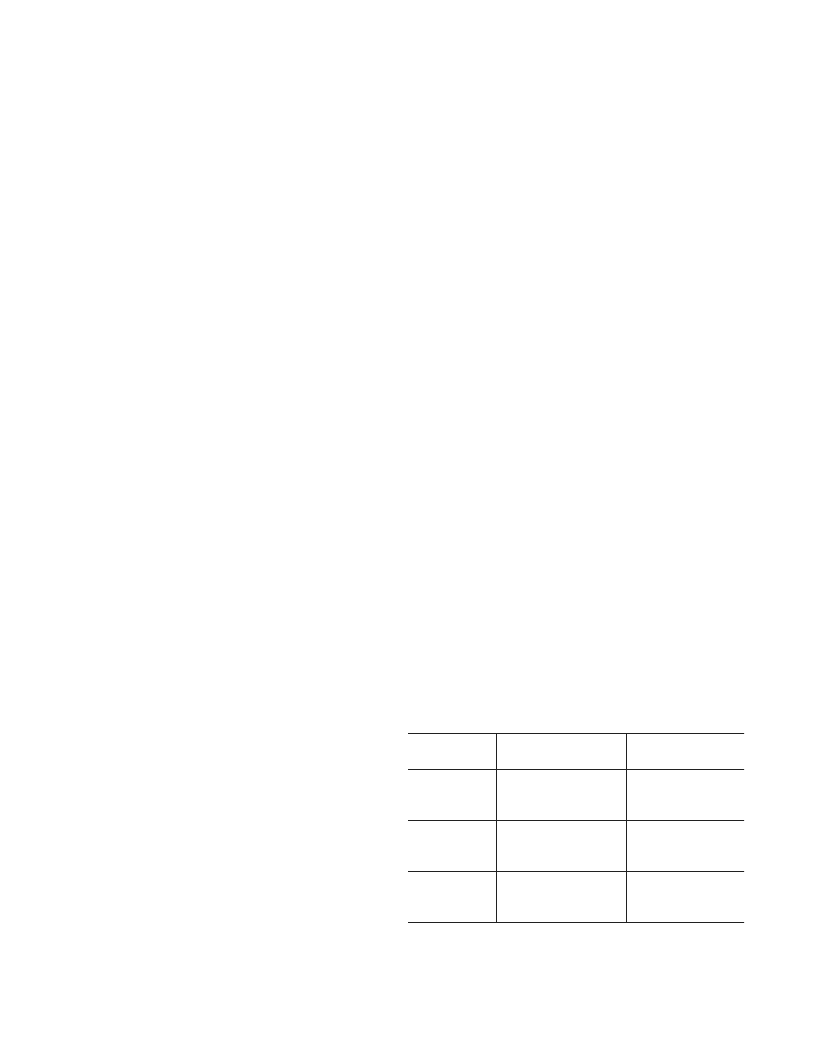

Table III. CLKOUT2 Timing Relative to CLKIN

In Alternative Operation Mode

DLL

Mult

CLKOUT2

Div Factor

CLKOUT2

1

1

2

4

CLKIN

CLKIN/2

CLKIN/4

2

1

2

4

2 CLKIN

CLKIN

CLKIN/2

4

1

2

4

4 CLKIN

2 CLKIN

CLKIN

相關PDF資料 |

PDF描述 |

|---|---|

| AD9862BST | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

| AD9864 | IF Digitizing Subsystem |

| AD9864-EB | IF Digitizing Subsystem |

| AD9864BCPZ | IF Digitizing Subsystem |

| AD9864BCPZRL | IF Digitizing Subsystem |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9862BST | 制造商:Analog Devices 功能描述:Mixed Signal Front End 128-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:12B MIXED SIGNAL FRONT END MXFE PROCESSO - Tape and Reel |

| AD9862BSTRL | 制造商:Analog Devices 功能描述:Mixed Signal Front End 128-Pin LQFP T/R 制造商:Rochester Electronics LLC 功能描述:12B MIXED SIGNAL FRONT END MXFE PROCESSO - Tape and Reel |

| AD9862BSTZ | 功能描述:IC FRONT-END MIXED-SGNL 128-LQFP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點:- 封裝/外殼:48-TQFP 裸露焊盤 供應商設備封裝:48-TQFP 裸露焊盤(7x7) 包裝:托盤 |

| AD9862BSTZRL | 功能描述:IC PROCESSOR FRONT END 128LQFP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點:- 封裝/外殼:48-TQFP 裸露焊盤 供應商設備封裝:48-TQFP 裸露焊盤(7x7) 包裝:托盤 |

| AD9862-EB | 制造商:Analog Devices 功能描述: 制造商:Analog Devices 功能描述:MIXED SIGNAL FRONT END - Bulk |

發布緊急采購,3分鐘左右您將得到回復。