- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄373969 > AD9862 (Analog Devices, Inc.) Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications PDF資料下載

參數(shù)資料

| 型號(hào): | AD9862 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

| 中文描述: | 混合寬帶通信信號(hào)前端(MxFE⑩)處理器 |

| 文件頁(yè)數(shù): | 7/32頁(yè) |

| 文件大小: | 617K |

| 代理商: | AD9862 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)

REV. 0

AD9860/AD9862

–7–

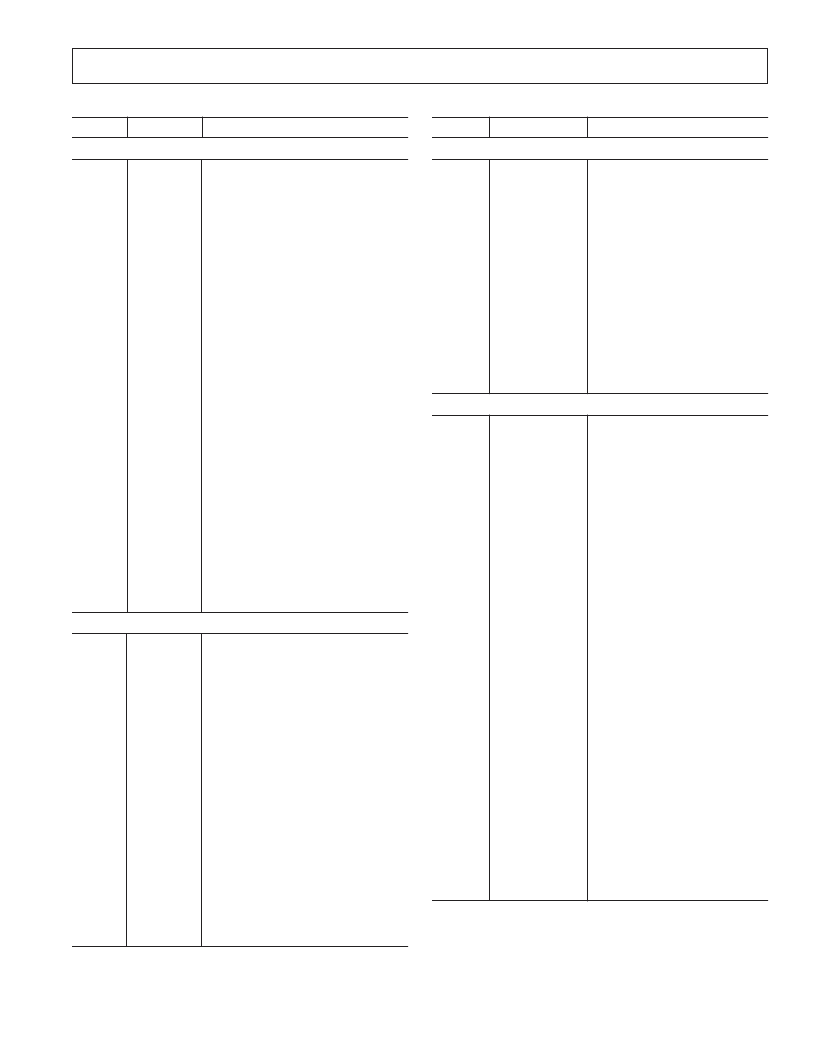

Pin No.

Mnemonic

Function

Clock Pins

10

11, 16

12

13

14

DLL_Lock

AGND

NC

AVDD

OSC1

DLL Lock Indicator Pin

DLL Analog Ground Pins

No Connect

DLL Analog Supply Pin

Single Ended Input Clock

(or Crystal Oscillator Input)

Crystal Oscillator Input

Controls CLKOUT1 Rate

Clock Output Generated from Input

Clock (DLL Multiplier Setting

and CLKOUT2 Divide Factor)

Clock Output Generated from

Input Clock (1 if CLKSEL = 1

or /2 if CLKSEL = 0)

15

17

64

OSC2

CLKSEL

CLKOUT2

65

CLKOUT1

Various Pins

1

3, 4, 13

2, 9

5

AUX_ADC_A1

AVDD

AGND

SIGDELT

Auxiliary ADC A Input 1

Analog Power Pins

Analog Ground Pins

Digital Output from

Programmable Sigma-Delta

Auxiliary DAC A Output

Auxiliary DAC B Output

Auxiliary DAC C Output

Digital Power Supply Pin

6

7

8

33, 36, 53, DVDD

59, 61, 66,

93

34, 35, 52, DGND

58, 60, 67,

94

54

55

56

57

63

95

AUX_DAC_A

AUX_DAC_B

AUX_DAC_C

Digital Ground Pin

SCLK

SDO

SDIO

SEN

RESETB

AUX_SPI_do

Serial Bus Clock Input

Serial Bus Data Bit

Serial Bus Data Bit

Serial Bus Enable

Reset (SPI Registers and Logic)

Optional Auxiliary ADC Serial Bus

Data Out Bit

Optional Auxiliary ADC Serial Bus

Data Out Latch Clock

Optional Auxiliary ADC Serial Bus

Chip Select Bit

Auxiliary ADC A Input 2

Auxiliary ADC B Input 1

Auxiliary ADC B Input 2

96

AUX_SPI_clk

97

AUX_SPI_csb

128

126

125

127

AUX_ADC_A2

AUX_ADC_B1

AUX_ADC_B2

AUX_ADC_REF Auxiliary ADC Reference

Pin No.

Mnemonic

Function

Receive Pins

68/70

–

79

D0A to

D9A/D11A

D0B to

D9B/D11B

RxSYNC

10-/12-Bit ADC Output of

Receive Channel A

10-/12-Bit ADC Output of

Receive Channel B

Synchronization Clock for

Channel A and Channel B Rx Paths

Analog Supply Pins

80/82

–

91

92

98, 99,

104, 105,

117, 118,

123, 124,

100, 103, AGND

106, 109,

110, 112,

113, 116,

119, 122,

101

AVDD

Analog Ground Pins

REFT_B

Top Reference Decoupling for

Channel B ADC

Bottom Reference Decoupling

for Channel B ADC

Receive Channel B Differential (+) Input

Receive Channel B Differential ( ) Input

Internal ADC Voltage Reference

Receive Channel A Differential ( ) Input

Receive Channel A Differential (+) Input

Bottom Reference Decoupling for

Channel A ADC

Top Reference Decoupling for

Channel A ADC

102

REFB_B

107

108

111

114

115

120

VIN+B

VIN

–

B

VREF

VIN

–

A

VIN+A

REFB_A

121

REFT_A

Transmit Pins

18, 20

23, 32

19, 24,

27, 28, 31

21

22

25

AVDD

Analog Supply Pins

AGND

Analog Ground Pins

REFIO

FSADJ

IOUT

–

A

Reference Output, 1.2 V Nominal

Full-Scale Current Adjust

Transmit Channel A DAC

Differential ( ) Output

Transmit Channel A DAC

Differential (+) Output

Transmit Channel B DAC

Differential (+) Output

Transmit Channel B DAC

Differential ( ) Output

12-/14-Bit Transmit DAC Data

(Interleaved Data when Required)

Synchronization Input for Transmitter

Configures Default Timing Mode,

TxBLANK

*

Controls Tx Digital Power Down

26

IOUT+A

29

IOUT+B

30

IOUT

–

B

37

–

48/50

Tx11/Tx13

to Tx0

TxSYNC

MODE/

51

62

*

The logic level of the Mode/TxBLANK pin at power up defines the default timing

mode; a logic low configures Normal Operation, logic high configures Alternate

Operation Mode.

PIN FUNCTION DESCRIPTIONS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9862BST | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

| AD9864 | IF Digitizing Subsystem |

| AD9864-EB | IF Digitizing Subsystem |

| AD9864BCPZ | IF Digitizing Subsystem |

| AD9864BCPZRL | IF Digitizing Subsystem |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9862BST | 制造商:Analog Devices 功能描述:Mixed Signal Front End 128-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:12B MIXED SIGNAL FRONT END MXFE PROCESSO - Tape and Reel |

| AD9862BSTRL | 制造商:Analog Devices 功能描述:Mixed Signal Front End 128-Pin LQFP T/R 制造商:Rochester Electronics LLC 功能描述:12B MIXED SIGNAL FRONT END MXFE PROCESSO - Tape and Reel |

| AD9862BSTZ | 功能描述:IC FRONT-END MIXED-SGNL 128-LQFP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點(diǎn):- 封裝/外殼:48-TQFP 裸露焊盤(pán) 供應(yīng)商設(shè)備封裝:48-TQFP 裸露焊盤(pán)(7x7) 包裝:托盤(pán) |

| AD9862BSTZRL | 功能描述:IC PROCESSOR FRONT END 128LQFP RoHS:是 類別:RF/IF 和 RFID >> RF 前端 (LNA + PA) 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:250 系列:- RF 型:GPS 頻率:1575.42MHz 特點(diǎn):- 封裝/外殼:48-TQFP 裸露焊盤(pán) 供應(yīng)商設(shè)備封裝:48-TQFP 裸露焊盤(pán)(7x7) 包裝:托盤(pán) |

| AD9862-EB | 制造商:Analog Devices 功能描述: 制造商:Analog Devices 功能描述:MIXED SIGNAL FRONT END - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。