- 您現在的位置:買賣IC網 > PDF目錄373969 > AD9864BCPZRL (ANALOG DEVICES INC) IF Digitizing Subsystem PDF資料下載

參數資料

| 型號: | AD9864BCPZRL |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費家電 |

| 英文描述: | IF Digitizing Subsystem |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, QCC48 |

| 封裝: | LEAD FREE, MO-220VKKD-2, LFCSP-48 |

| 文件頁數: | 17/44頁 |

| 文件大小: | 1984K |

| 代理商: | AD9864BCPZRL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

AD9864

THEORY OF OPERATION

SERIAL PORT INTERFACE (SPI)

The serial port of the AD9864 has 3-wire or 4-wire SPI capabil-

ity, allowing read/write access to all registers that configure the

device’s internal parameters. The default 3-wire serial commu-

nication port consists of a clock (PC), peripheral enable (PE),

and bidirectional data (PD) signal. The inputs to PC, PE, and

PD contain a Schmitt trigger with a nominal hysteresis of 0.4 V

centered about the digital interface supply, i.e., VDDH/2.

A 4-wire SPI interface can be enabled by setting the MSB of the

SSICRB register (Reg. 0x19, Bit 7) and setting Reg. 0x3A to 00,

resulting in the output data appearing on the DOUTB pin.

Note that since the default power-up state sets DOUTB low,

bus contention is possible for systems sharing the SPI output

line. To avoid any bus contention, the DOUTB pin can be

three-stated by setting the fourth control bit in the three-state

bit (Reg. 0x3B, Bit 3). This bit can then be toggled to gain access

to the shared SPI output line. An 8-bit instruction header must

accompany each read and write SPI operation. Only the write

operation supports an auto-increment mode, which allows the

entire chip to be configured in a single write operation. The

instruction header is shown in Table 7. It includes a read/not-

write indicator bit, six address bits, and a Don’t Care bit. The

data bits immediately follow the instruction header for both

read and write operations. Note that the address and data are

always given MSB first.

Table 7. Instruction Header Information

MSB

I7

I6

I5

I4

R/W

A5

A4

A3

Rev. 0 | Page 17 of 44

I3

A2

I2

A1

I1

A0

LSB

I0

X

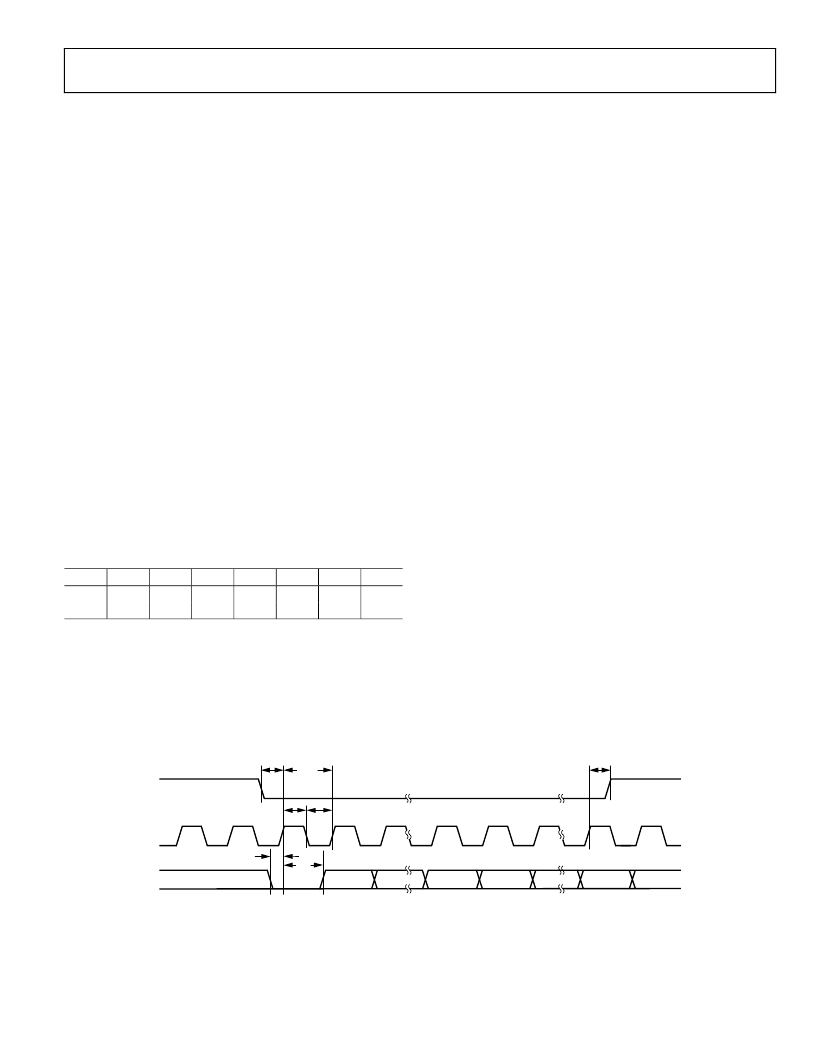

Figure 29 illustrates the timing requirements for a write opera-

tion to the SPI port. After the peripheral enable (PE) signal goes

low, data (PD) pertaining to the instruction header is read on

the rising edges of the clock (PC). To initiate a write operation,

the read/not-write bit is set low. After the instruction header is

read, the eight data bits pertaining to the specified register are

shifted into the data pin (PD) on the rising edges of the next

eight clock cycles. PE stays low during the operation and goes

high at the end of the transfer. If PE rises before the eight clock

cycles have passed, the operation is aborted. If PE stays low for

an additional eight clock cycles, the destination address is

incremented and another eight bits of data are shifted in.

Again, should PE rise early, the current byte is ignored. By

using this implicit addressing mode, the chip can be configured

with a single write operation. Registers identified as being sub-

ject to frequent updates, namely those associated with power

control and AGC operation, have been assigned adjacent

addresses to minimize the time required to update them. Note

that multibyte registers are big endian (the most significant

byte has the lower address) and are updated when a write to the

least significant byte occurs.

Figure 30 illustrates the timing for a read operation to the SPI

port. Although the AD9864 does not require read access for

proper operation, it is often useful in the product development

phase or for system authentication. Note that the read-back

enable bit (Register 0x3A, Bit 3) must be set for a read opera-

tion with a 3-wire SPI interface. After the peripheral enable

(PE) signal goes low, data (PD) pertaining to the instruction

header is read on the rising edges of the clock (PC). A read

operation occurs if the read/not-write indicator is set high.

After the address bits of the instruction header are read, the

eight data bits pertaining to the specified register are shifted out

of the data pin (PD) on the falling edges of the next eight clock

cycles. If the 4-wire SPI interface is enabled, the eight data bits

will also appear on the DOUTB pin with the same timing rela-

tionship as those appearing at PD. After the last data bit is

shifted out, the user should return PE high, causing PD to

become three-stated and return to its normal status as an input

pin. Since the auto-increment mode is not supported for read

operations, an instruction header is required for each register

read operation and PE must return high before initiating the

next read operation.

PE

PC

PD

t

H

t

DS

t

HI

t

S

t

DH

t

LOW

t

CLK

R/W

A5

A4

A0

D7

D6

D1

D0

DON'T

CARE

0

Figure 29.

SPI Write Operation Timing

相關PDF資料 |

PDF描述 |

|---|---|

| AD9866BCPRL | Broadband Modem Mixed Signal Front End |

| AD9866CHIPS | Broadband Modem Mixed Signal Front End |

| AD9866 | Broadband Modem Mixed Signal Front End |

| AD9866-EB | Broadband Modem Mixed Signal Front End |

| AD9866BCP | Broadband Modem Mixed Signal Front End |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9864-EB | 制造商:Analog Devices 功能描述: |

| AD9864-EBZ | 功能描述:BOARD EVAL FOR AD9864 制造商:analog devices inc. 系列:- 零件狀態:有效 類型:數字轉換器 頻率:10MHz ~ 300MHz 配套使用產品/相關產品:AD9864 所含物品:板 標準包裝:1 |

| AD9865 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9865BCP | 制造商:Analog Devices 功能描述:Mixed Signal Front End 64-Pin LFCSP EP 制造商:Analog Devices 功能描述:MIXED SGNL FRONT END 64LFCSP EP - Trays 制造商:Analog Devices 功能描述:10BIT MIXED SIGNAL CONVERTER 9865 |

| AD9865BCPRL | 制造商:Analog Devices 功能描述:Mixed Signal Front End 64-Pin LFCSP EP T/R |

發布緊急采購,3分鐘左右您將得到回復。