- 您現在的位置:買賣IC網 > PDF目錄382723 > UJA1065 (NXP Semiconductors N.V.) High-speed CAN/LIN fail-safe system basis chip PDF資料下載

參數資料

| 型號: | UJA1065 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | High-speed CAN/LIN fail-safe system basis chip |

| 中文描述: | 高速的CAN / LIN故障防護系統基礎芯片 |

| 文件頁數: | 54/67頁 |

| 文件大小: | 285K |

| 代理商: | UJA1065 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁當前第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁

9397 750 14409

Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Objective data sheet

Rev. 01 — 10 August 2005

54 of 67

Philips Semiconductors

UJA1065

High-speed CAN/LIN fail-safe system basis chip

[1]

V

V1(nom)

is 3 V, 3.3 V or 5 V, depending on the SBC version.

Not tested in production.

[2]

[3]

V2 internally supplies the SBC CAN transceiver. The performance of the CAN transceiver can be impaired if V2 is also used to supply

other circuitry while the CAN transceiver is in use.

9.

Dynamic characteristics

Temperature detection

T

j(warn)

high junction

temperature warning

level

160

175

190

°

C

Table 26:

T

vj

=

40

°

C to +150

°

C, V

BAT42

= 5.5 V to 52 V and V

BAT14

= 5.5 V to 27 V unless otherwise specified. All voltages are

defined with respect to ground. Positive currents flow into the IC. All parameters are guaranteed over the virtual junction

temperature range by design. Products are 100 % tested at 125

°

C ambient temperature on wafer level (pre-testing). Cased

products are 100 % tested at 25

°

C ambient temperature (final testing). Both pre-testing and final testing use correlated test

conditions to cover the specified temperature and power supply voltage range.

Symbol

Parameter

Conditions

Characteristics

…continued

Min

Typ

Max

Unit

Table 27:

T

vj

=

40

°

C to + 150

°

C; V

BAT42

= 5.5 V to 52 V; V

BAT14

= 5.5 V to 27 V; unless otherwise specified. All voltages are defined

with respect to ground. Positive currents flow into the IC. All parameters are guaranteed over the virtual junction temperature

range by design. Products are 100 % tested at 125

°

C ambient temperature on wafer level (pre-testing). Cased products are

100 % tested at 25

°

C ambient temperature (final testing). Both pre-testing and final testing use correlated test conditions to

cover the specified temperature and power supply voltage range.

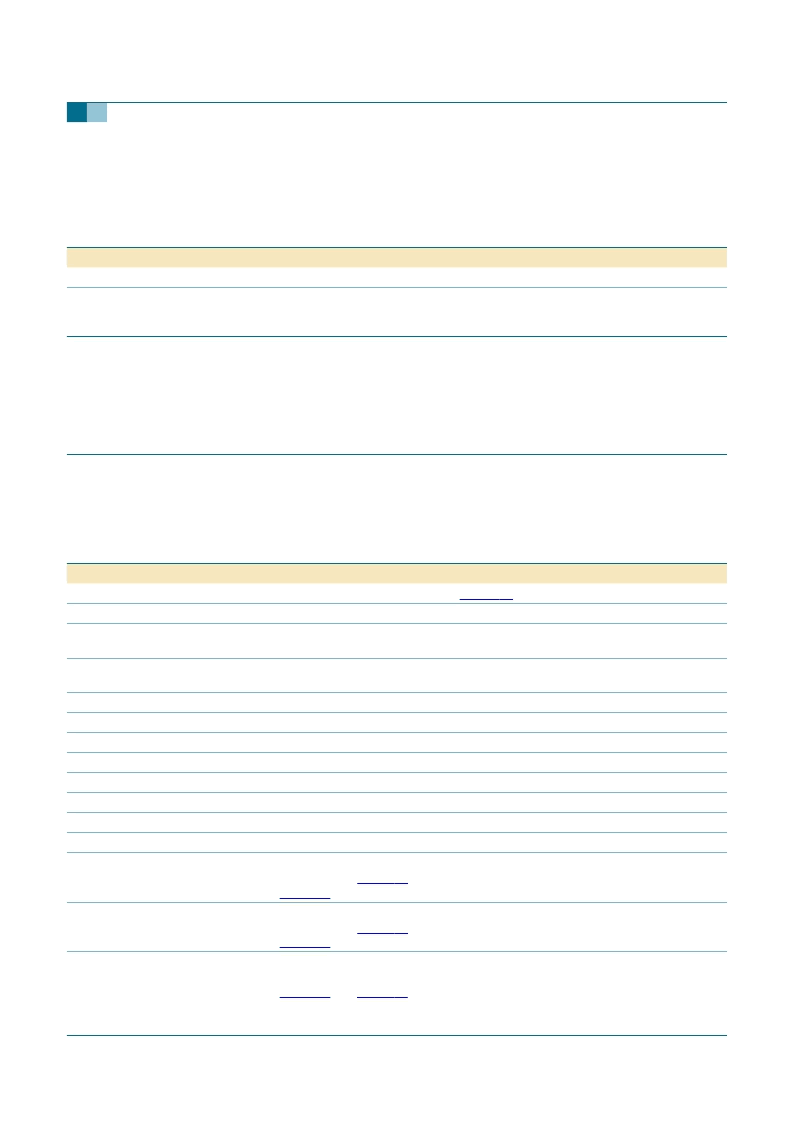

Symbol

Parameter

Conditions

Serial peripheral interface timing; pins SCS, SCK, SDI and SDO (see

Figure 21

)

T

cyc

clock cycle time

t

lead

enable lead time

clock is low when SPI select

falls

t

lag

enable lag time

clock is low when SPI select

rises

t

SCKH

clock HIGH time

t

SCKL

clock LOW time

t

su

input data setup time

t

h

input data hold time

t

DOV

output data valid time pin SDO, C

L

= 10 pF

t

SSH

SPI select HIGH time

t

SSL

SPI select LOW time

CAN transceiver timing; pins CANL, CANH, TXDC and RXDC

t

t(reces-dom)

output transition time

recessive to dominant

R = 60

; see

Figure 17

and

Figure 18

t

t(dom-reces)

output transition time

dominant to recessive

R = 60

; see

Figure 17

and

Figure 18

t

PHL

propagation delay

TXDC to RXDC

(HIGH-to-LOW

transition)

Characteristics

Min

Typ

Max

Unit

480

240

-

-

-

-

ns

ns

240

-

-

ns

190

190

100

100

-

200

200

-

-

-

-

-

-

-

-

-

-

-

100

-

-

ns

ns

ns

ns

ns

ns

ns

10 % to 90 %; C = 100 pF;

-

100

-

ns

90 % to 10 %; C = 100 pF;

-

100

-

ns

50 % V

TXDC

to 50 % V

RXDC

;

C = 100 pF; R = 60

; see

Figure 17

and

Figure 18

-

150

220

ns

相關PDF資料 |

PDF描述 |

|---|---|

| UL631H256 | SimtekLow Voltage SoftStore 32K x 8 nvSRAM |

| UL631H256S2C35 | SimtekLow Voltage SoftStore 32K x 8 nvSRAM |

| UL631H256S2C35G1 | SimtekLow Voltage SoftStore 32K x 8 nvSRAM |

| UL631H256S2C45 | SimtekLow Voltage SoftStore 32K x 8 nvSRAM |

| UL631H256S2K35 | SimtekLow Voltage SoftStore 32K x 8 nvSRAM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| UJA1065TW | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:High-speed CAN/LIN fail-safe system basis chip |

| UJA1065TW/3V0 | 功能描述:網絡控制器與處理器 IC HI SPEED CAN SYSTEM RoHS:否 制造商:Micrel 產品:Controller Area Network (CAN) 收發器數量: 數據速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| UJA1065TW/3V0,512 | 功能描述:CAN 接口集成電路 HI SPEED CAN SYSTEM RoHS:否 制造商:Texas Instruments 類型:Transceivers 工作電源電壓:5 V 電源電流: 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:SOIC-8 封裝:Tube |

| UJA1065TW/3V0,518 | 功能描述:網絡控制器與處理器 IC HI SPEED CAN SYSTEM RoHS:否 制造商:Micrel 產品:Controller Area Network (CAN) 收發器數量: 數據速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| UJA1065TW/3V0512 | 制造商:NXP Semiconductors 功能描述:CONTROLLER SYS CAN/LIN 3V 32HTSSOP |

發布緊急采購,3分鐘左右您將得到回復。