- 您現在的位置:買賣IC網 > PDF目錄373973 > AD9992BBCZRL (ANALOG DEVICES INC) 12-Bit CCD Signal Processor with Precision Timing Generator PDF資料下載

參數資料

| 型號: | AD9992BBCZRL |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費家電 |

| 英文描述: | 12-Bit CCD Signal Processor with Precision Timing Generator |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PBGA105 |

| 封裝: | 8 X 8 MM, 0.65 MM PITCH, ROHS COMPLIANT, MO-225, CSPBGA-105 |

| 文件頁數: | 67/92頁 |

| 文件大小: | 718K |

| 代理商: | AD9992BBCZRL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁當前第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

AD9992

Rev. 0 | Page 67 of 92

VD

HD

CLI

X

X

X

X

X

X

X

X

3ns MIN

X

X

X

X

X

X

X

X

X

X

X

X

X

3ns MIN

t

CLIDLY

35.5 CYCLES

X

X

X

0

X

X

X

X

X

X

X

X

X

X

X

X

X

1

2

NOTES

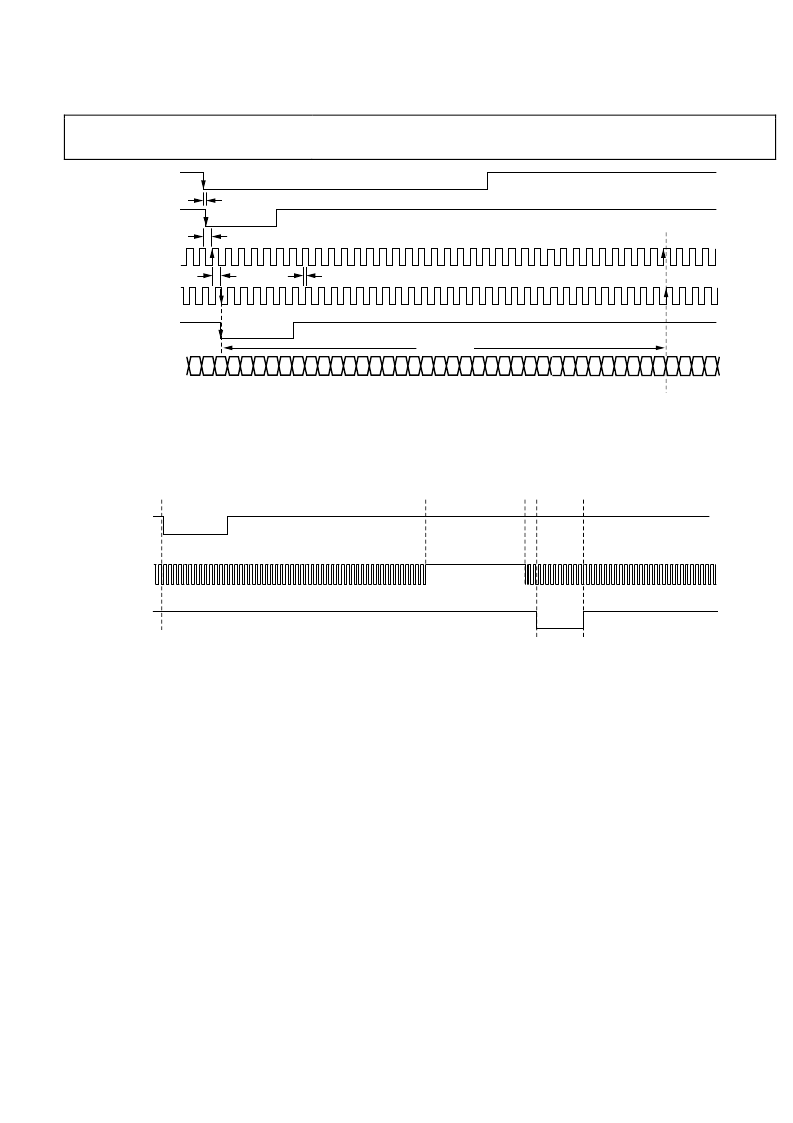

1. EXTERNAL HD FALLING EDGE IS LATCHED BY CLI RISING EDGE, AND THEN LATCHED AGAIN BY SHD INTERNAL FALLING EDGE.

2. INTERNAL H-COUNTER IS ALWAYS RESET 35.5 CLOCK CYCLES AFTER THE INTERNAL HD FALLING EDGE.

3. DEPENDING ON THE VALUE OF SHDLOC, H-COUNTER RESET CAN OCCUR 36 OR 37 CLI CLOCK EDGES AFTER THE EXTERNAL HD FALLING EDGE.

4. SHDLOC = 0 IS SHOWN IN ABOVE EXAMPLE. IN THIS CASE, THE H-COUNTER RESET OCCURS 36 CLI RISING EDGES AFTER HD FALLING EDGE.

5. HD FALLING EDGE SHOULD OCCUR COINCIDENT WITH VD FALLING EDGE (WITHIN SAME CLI CYCLE) OR AFTER VD FALLING EDGE. HD FALLING

EDGE SHOULD NOT OCCUR WITHIN FIVE CLI CYCLES PRIOR TO THE VD FALLING EDGE.

Figure 75. External VD/HD and Internal H-Counter Synchronization, Slave Mode

H-COUNTER

RESET

SHD

INTERNAL

HD

INTERNAL

H-COUNTER

(PIXEL COUNTER)

t

VDHD

0

1

HBLKTOG1

2

HBLKTOG2

3

CLPOB_TOG1

4

CLPOB_TOG2

60

100

103

112

(60 – 36) = 24

(100 – 36) = 64

(103 – 36) = 67

(112 – 36) = 76

MASTER MODE

SLAVE MODE

H1

CLPOB

PIXEL NO.

HD

112

103

100

60

0

1

2

3

4

0

Figure 76. Example of Slave Mode Register Setting to Obtain Desired Toggle Positions

Vertical Toggle Position Placement Near Counter Reset

An additional consideration during the reset of the internal

counters is the vertical toggle position placement. Prior to the

internal counters being reset, there is a region of 36 pixels

during which no toggle positions should be programmed.

As shown in Figure 77, for master mode the last 36 pixels before

the HD falling edge must not be used for toggle position placement

of the V, VSG, SUBCK, HBLK, PBLK, or CLPOB pulses.

Figure 78 shows the same example for slave mode. The same

restriction applies: the last 36 pixels before the counters are

reset cannot be used. However, in slave mode, the counter reset

is delayed with respect to VD/HD placement, so the inhibited

area is different than it is in master mode.

It is recommended that Pixel Location 0 not be used for any of

the toggle positions for the VSG and SUBCK pulses.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9995KCP | 12-Bit CCD Signal Processor with Precision Timing ⑩ Generator |

| AD9995KCPRL | 12-Bit CCD Signal Processor with Precision Timing ⑩ Generator |

| AD9995 | 12-Bit CCD Signal Processor with Precision Timing ⑩ Generator |

| ADA4000-2ARMZ-RL | Low Cost, Precision JFET Input Operational Amplifiers |

| ADA4000-1 | Low Cost, Precision JFET Input Operational Amplifiers |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9993BBCZ | 功能描述:IC MIXED-SIGNAL FRONT END 196BGA 制造商:analog devices inc. 系列:- 包裝:托盤 零件狀態:在售 類型:ADC,DAC 輸入類型:LVDS 輸出類型:LVDS 接口:SPI 電流 - 電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:196-LFBGA,CSPBGA 供應商器件封裝:196-CSPBGA(12x12) 標準包裝:1 |

| AD9993BBCZRL | 功能描述:IC MIXED-SIGNAL FRONT END 196BGA 制造商:analog devices inc. 系列:- 包裝:帶卷(TR) 零件狀態:在售 類型:ADC,DAC 輸入類型:LVDS 輸出類型:LVDS 接口:SPI 電流 - 電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:196-LFBGA,CSPBGA 供應商器件封裝:196-CSPBGA(12x12) 標準包裝:1,500 |

| AD9993-EBZ | 功能描述:EVAL BOARD MXFE AD9993 制造商:analog devices inc. 系列:* 零件狀態:在售 標準包裝:1 |

| AD9994 | 制造商:AD 制造商全稱:Analog Devices 功能描述:12-Bit CCD Signal Processor with Precision Timing Generator |

| AD9994BCP | 制造商:Analog Devices 功能描述:AFE GEN PURPOSE 12-BIT 64LFCSP - Bulk |

發布緊急采購,3分鐘左右您將得到回復。