- 您現在的位置:買賣IC網 > PDF目錄379644 > ADC82124 (Electronic Theatre Controls, Inc.) 24 Ports 10/100 Fast Ethernet Switch Controller PDF資料下載

參數資料

| 型號: | ADC82124 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 24 Ports 10/100 Fast Ethernet Switch Controller |

| 中文描述: | 24端口10/100快速以太網開關控制器 |

| 文件頁數: | 16/48頁 |

| 文件大小: | 411K |

| 代理商: | ADC82124 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

16

A

I

D

7. REGISTER DESCRIPTION

Registers in the ACD82124 are used to define the op-

eration mode of various function modules of the switch

controller and the peripheral devices. Default values at

power-on are defined by the factory. The manage-

ment CPU (optional) can read the content of all regis-

ters and modify some of the registers to change the

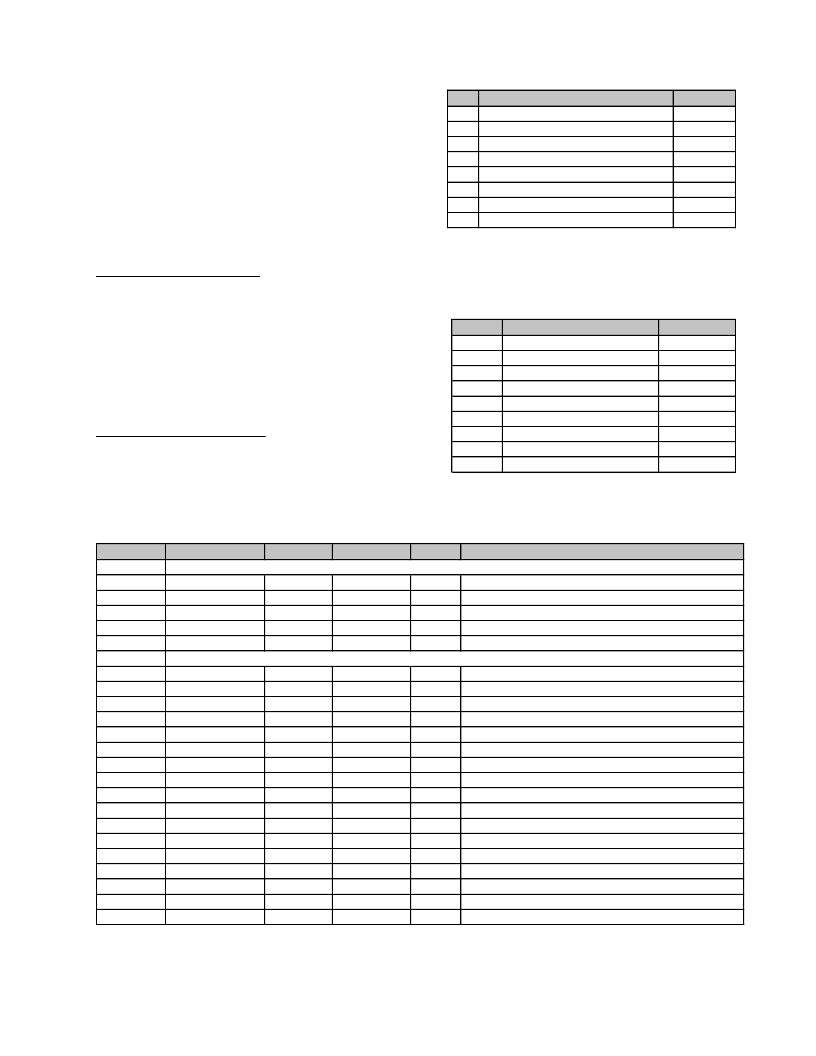

operation mode. Table-7.0 lists all the registers inside

the switch controller.

INTSRC register (register 1)

The INTSRC register indicates the source of the inter-

rupt request. Before the CPU starts to respond to an

interrupt request, it should read this register to find out

the interrupt source. This register is automatically

cleared after each read. Table-7.1 lists all the bits of

this register.

SYSERR register (register 2)

The SYSERR register indicates the presence of sys-

tem errors. It is automatically cleared after each read.

Table-7.2 lists all kind of system error.

Table-7.1: INTSRC Register

Bit

0

System initialization completed

1

System error occurred

2

Port partition occurred

3

ARL Interrupt

4

Reserved

5

Reserved

6

Reserved

7

Reserved

Description

Default

0

0

0

0

0

0

0

0

Table-7.2: SYSERR Register

Bit

0

BIST failure indication

1

2

3

4

5

6

7

8

Description

Default

0

0

0

0

0

0

0

0

0

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Table-7.0: Register List

Address

0

1

2

3

4

5

6-15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32-63

Name

Type

Size

Depth

Reserved

Description

INTSRC

SYSERR

PAR

PMERR

ACT

R

R

R

R

R

8 Bit

24 Bit

24 Bit

24 Bit

24 Bit

1

1

1

1

1

Reserved

Interrupt Source

System Error

Port Partition Indication

PHY Management Error

Port Avtivity

SYSCFG

INTMSK

SPEED

LINK

nFWD

nBP

nPORT

PVID

VPID

POSCFG

nPAUSE

DPLX

RVSMII

nPM

ERRMSK

CLKADJ

PHYREG

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

16 Bit

8 Bit

24 Bit

24 Bit

24 Bit

24 Bit

24 Bit

4 Bit

5 Bit

19 Bit

24 Bit

24 Bit

5 Bit

24 Bit

8 Bit

4 Bit

16 Bit

1

1

1

1

1

1

1

24

4

1

1

1

1

1

1

1

24

System Configuration

Interrupt Mask

Port Speed

Port Link

Port Forward Disable

Port Back Pressure Disable

Port Disable

Port VLAN ID

VLAN Dumping Port

Power-On-Strobe Configuration

Port Pause Frame Disable

Port Duplex Mode

Reversed MII Selection

Port PHY Management Disable

Error Mask

ARL Clock Delay Adjustment

Registers in PHY device, (REG# - 32)

相關PDF資料 |

PDF描述 |

|---|---|

| ADEX-10L | Frequency Mixer Level 4 (LO Power +4 dBm) 10 to 1000 MHz |

| ADL-65055SA2 | Perfect Solution For Auto Power Controlled Laser Diode |

| ADM200 | Related Products: Motor Operated Auto Drain |

| ADM200-031- | Related Products: Motor Operated Auto Drain |

| ADM200-031-4 | Related Products: Motor Operated Auto Drain |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADC-825MC | 制造商:Murata Power Solutions 功能描述:Analog to Digital Converter |

| ADC-825MM | 制造商:Murata Power Solutions 功能描述:Analog to Digital Converter |

| ADC-826MC | 制造商:Murata Power Solutions 功能描述:Analog to Digital Converter |

| ADC-826MM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog-to-Digital Converter, 10-Bit |

| ADC-827AMC | 制造商:Murata Power Solutions 功能描述:Analog to Digital Converter |

發布緊急采購,3分鐘左右您將得到回復。