- 您現在的位置:買賣IC網 > PDF目錄373970 > AD9910 (Analog Devices, Inc.) 1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer PDF資料下載

參數資料

| 型號: | AD9910 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | XO, clock |

| 英文描述: | 1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer |

| 中文描述: | 1 GSPS的,14位,3.3伏的CMOS直接數字頻率合成 |

| 文件頁數: | 41/60頁 |

| 文件大小: | 764K |

| 代理商: | AD9910 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當前第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

AD9910

ADDITIONAL FEATURES

PROFILES

The AD9910 supports the use of profiles, which consist of a group

of eight registers containing pertinent operating parameters for

a particular operating mode. Profiles enable rapid switching

between parameter sets. Profile parameters are programmed via

the serial I/O port. Once programmed, a specific profile is

activated by means of three external pins (PROFILE<2:0>). A

particular profile is activated by providing the appropriate logic

levels to the profile control pins per Table 15.

Rev. 0 | Page 41 of 60

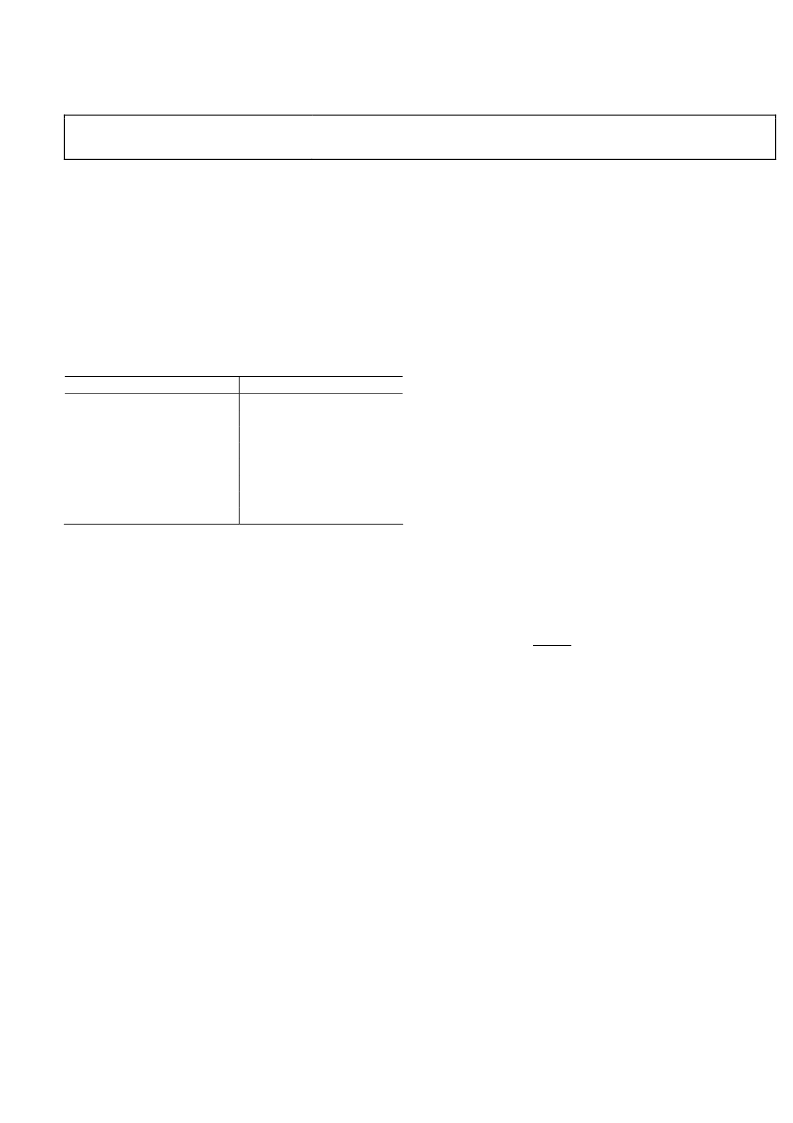

Table 15. Profile Control Pins

PROFILE<2:0>

000

001

010

011

100

101

110

111

Active Profile

0

1

2

3

4

5

6

7

There are two different parameter sets that the eight profile

registers can control depending on the operating mode of the

device. When RAM enable = 0, the profile parameters follow

the single tone profile format detailed in the Register Map and

Bit Descriptions section. When RAM enable = 1, they follow

the RAM profile format.

As an example of the use of profiles, consider an application for

implementing basic two-tone frequency shift keying (FSK). FSK

uses the binary data in a serial bit stream to select between two

different frequencies: a mark frequency (Logic 1) and a space

frequency (Logic 0). To accommodate FSK, the device operates

in single tone mode. The register, Single Tone Profile 0, is

programmed with the appropriate frequency tuning word for a

space. The register, Single Tone Profile 1, is programmed with

the appropriate frequency tuning word for a mark. Then, with

the PROFILE1 and PROFILE2 pins tied to Logic 0, the

PROFILE0 pin is connected to the serial bit stream. In this way,

the logic state of the PROFILE0 pin causes the appropriate mark

and space frequencies to be generated in accordance with the

binary digits of the bit stream.

I/O_UPDATE PIN

By default, the I/O_UPDATE pin is an input that serves as a

strobe signal to allow synchronous update of the device

operating parameters. For example, frequency, phase and

amplitude control words for the DDS may be programmed via

the serial I/O Port. However, the serial I/O Port is an

asynchronous interface, so programming of the device

operating parameters via the I/O port is not synchronized with

the internal timing. With the I/O_UPDATE pin, the user can

synchronize the application of certain programmed operating

parameters with external circuitry when new parameters are

programmed into the I/O registers. A rising edge on I/O_UPDATE

initiates transfer of the register contents to the internal workings

of the device. Alternatively, the transfer of programmed data

from the programming registers to the internal hardware can

be accomplished by changing the state of the profile pins.

AUTOMATIC I/O UPDATE

The AD9910 offers an option whereby the I/O update function

is asserted automatically rather than relying on an external signal

supplied by the user. This feature is enabled by setting the internal

I/O update active bit in Control Function Register 2 (CFR2).

When this feature is active, the I/O_UPDATE pin becomes

an output pin. It generates an active high pulse each time an

internal I/O update occurs. The duration of the pulse is

approximately 12 cycles of SYSCLK. This I/O update strobe

can be used to notify an external controller that the device

has generated an I/O update internally.

The repetition rate of the internal I/O Update is programmed

via the serial I/O port. There are two parameters that control

the repetition rate. The first consists of the two I/O update rate

control bits in CFR2. The second is the 32-bit word in the I/O

update rate register that sets the range of an internal counter.

The I/O update rate control bits establish a divide by 1, 2, 4, or 8

of a clock signal that runs at f

SYSCLK

. The output of the divider

clocks the aforementioned 32-bit internal counter. The

repetition rate of the I/O update is given by

f

f

A

Update

O

I

2

B

SYSCLK

_

/

=

where

A

is the value of the 2-bit word comprising the I/O

update rate control bits and

B

is the value of the 32-bit word

stored in the I/O update rate register. The default value of A is 0

and the value of B is 0xFFFF. If B is programmed to 0x0003 or

less, the I/O_UPDATE pin no longer pulses, but assumes a

static Logic 1 state.

POWER-DOWN CONTROL

The AD9910 offers the ability to independently power down

four specific sections of the device. Power-down functionality

applies to the

Digital core

DAC

Auxiliary DAC

Input REFCLK clock circuitry

A power-down of the digital core disables the ability to update

the serial I/O port. However, the digital power-down bit can

still be cleared via the serial port to prevent the possibility of a

non-recoverable state.

Software power-down is controlled via four independent

power-down bits in Control Function Register 1 (CFR1).

相關PDF資料 |

PDF描述 |

|---|---|

| AD9910_07 | 1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer |

| AD9910BSVZ | 1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer |

| AD9910BSVZ-REEL | 1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer |

| AD9912 | 1 GSPS Direct Digital Synthesizer w/ 14-bit DAC |

| AD9913 | Low Power 250 MSPS 10-Bit DAC 1.8 V CMOS Direct Digital Synthesizer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9910/PCBZ | 功能描述:數據轉換 IC 開發工具 1GSPS 14 bit DDS w/ parallel input port RoHS:否 制造商:Texas Instruments 產品:Demonstration Kits 類型:ADC 工具用于評估:ADS130E08 接口類型:SPI 工作電源電壓:- 6 V to + 6 V |

| AD9910_07 | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS, 14-Bit, 3.3 V CMOS Direct Digital Synthesizer |

| AD9910BSVZ | 功能描述:IC DDS 1GSPS 14BIT PAR 100TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 直接數字合成 (DDS) 系列:- 產品變化通告:Product Discontinuance 27/Oct/2011 標準包裝:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 調節字寬(位):32 b 電源電壓:2.97 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:帶卷 (TR) |

| AD9910BSVZ | 制造商:Analog Devices 功能描述:IC DDS 1GHZ TQFP-100 制造商:Analog Devices 功能描述:IC, DDS, 1GHZ, TQFP-100 |

| AD9910BSVZ-REEL | 功能描述:IC DDS 1GSPS 14BIT PAR 100TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 直接數字合成 (DDS) 系列:- 產品變化通告:Product Discontinuance 27/Oct/2011 標準包裝:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 調節字寬(位):32 b 電源電壓:2.97 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:帶卷 (TR) |

發布緊急采購,3分鐘左右您將得到回復。